Материалы по тегу: fpga

|

04.05.2022 [21:29], Алексей Степин

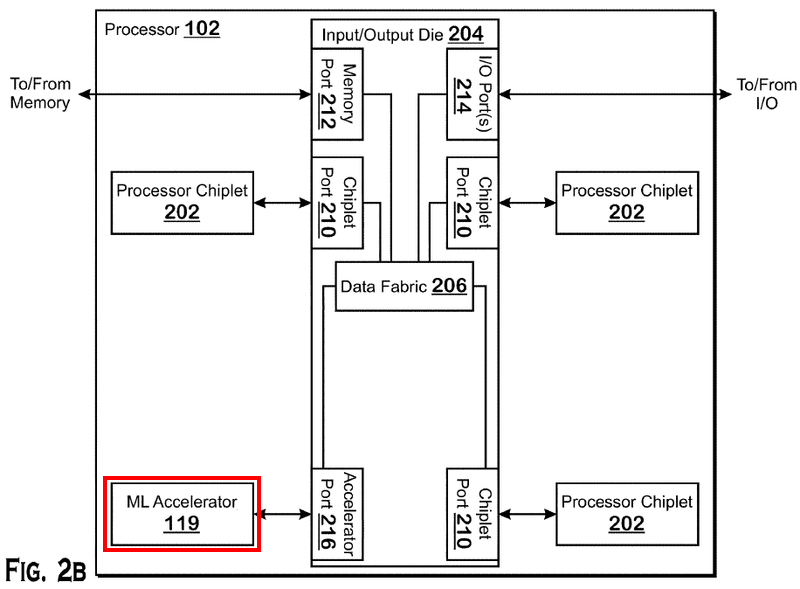

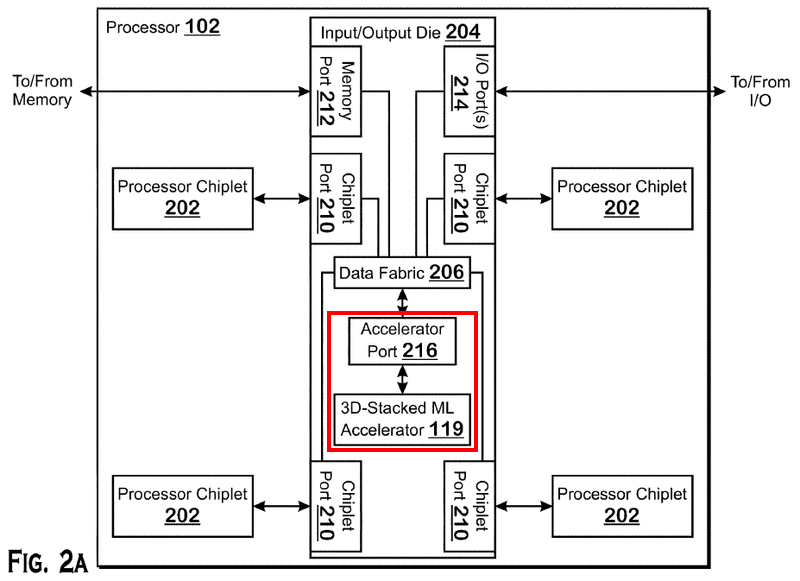

AMD предложила внедрить в процессоры EPYC ИИ-ускорители на базе FPGA XilinxМодульный подход к компоновке процессоров имеет как недостатки, так и преимущества. К первым относится ограниченность межъядерной коммуникации, а ко вторым — возможность легко регулировать количество чиплетов в процессорах, предназначенных для разных сегментов рынка. AMD пошла ещё дальше — теперь чиплеты получили уникальную возможность установки дополнительного кеша сверху основного кристалла (3D V-Cache в Milan-X), а вскоре появятся и чиплеты, включающие не только ядра CPU. В попытках сделать как можно более универсальный процессор тоже видны два подхода. Intel уповает на инструкции AVX-512, которые получили расширения VNNI для работы с актуальными ИИ-нагрузками. А вскоре к ним добавится ещё и набор AMX. Базовый набор инструкций у AMD не менялся уже достаточно давно, но будущие EPYC вскоре тоже получат возможность работы с ИИ-задачам, как раз благодаря модульной компоновке. Новые патенты AMD говорят о сочетании CPU- и FPGA-чиплетов поглощённой ранее Xilinx в одной SoC. Патенты покрывают два способа интеграции новых кристаллов : либо добавлением нового чиплета по соседству с другими, либо использование 3D-стекинга как в случае с 3D V-Cache. В последнем случае возникают некоторые трудности с теплоотводом при размещении ускорителей непосредственно над CPU-чиплетами, поэтому AMD предлагает устанавливать новые чипы на IO-модуль.  Новые процессоры AMD EPYC, имеющие гетерогенную чиплетную архитектуру должны увидеть свет уже в 2023 году в поколении Zen 4 в виде 5-нм платформ Genoa (до 96 ядер) и Bergamo (128 ядер). И это только начало, ведь ничто не мешает использовать и другие виды чиплетов, от GPU и DPU до специфических DSP и даже ASIC. Впрочем, скорее всего, подобные чипы будут востребованы относительно небольшим числом клиентов или вообще будут создавать на заказ, как это ранее уже произошло с Intel.  Первые гибридные процессоры Xeon с FPGA компании Altera, которую Intel в итоге купила годом позже, были анонсированы ещё в 2014 году. По неофициальным данным, эти чипы создавались для обслуживания и ускорения работы СУБД Oracle. Следующая попытка была предпринята уже в поколении Skylake-SP. Тогда появился чип Intel Xeon Gold 6138P с ПЛИС Arria 10 GX 1150, соединённой с ядрами процессора посредством UPI. Одна из сфер его применение — телекоммуникации.

16.10.2020 [23:17], Юрий Поздеев

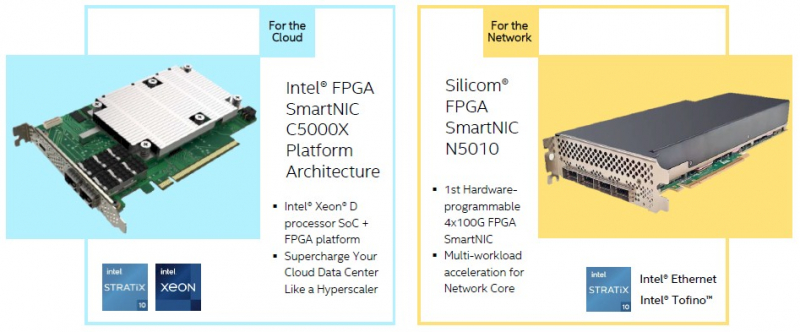

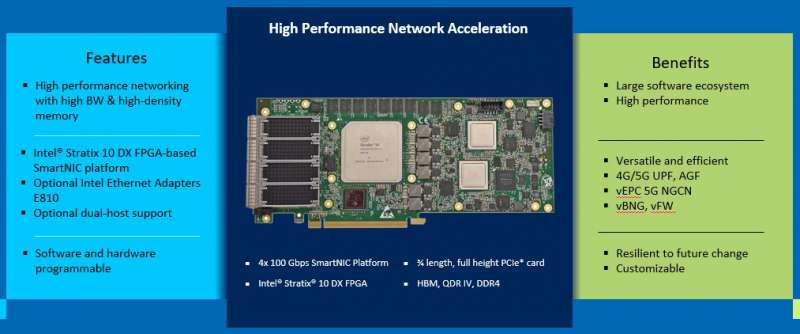

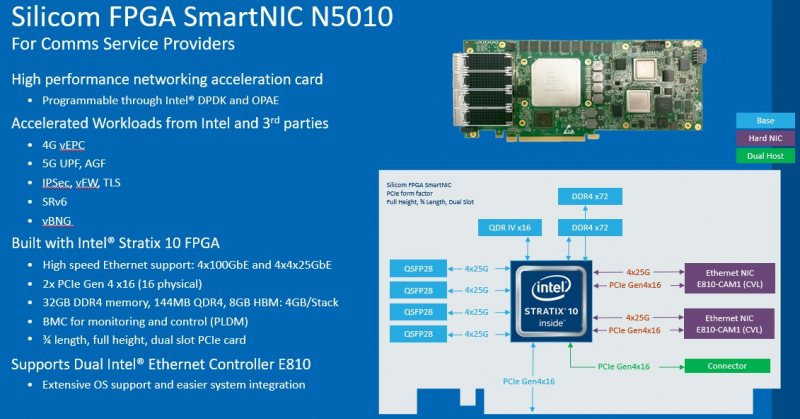

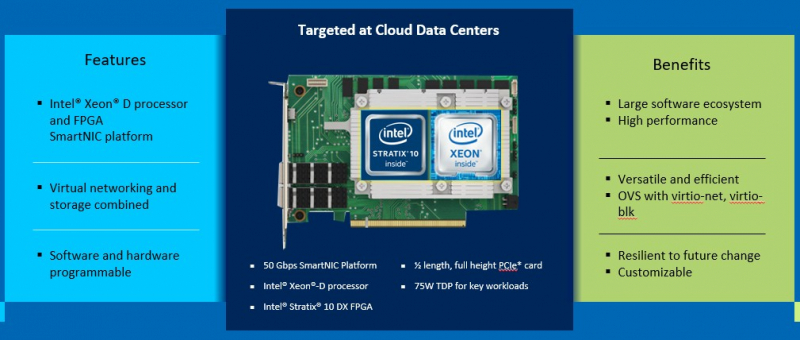

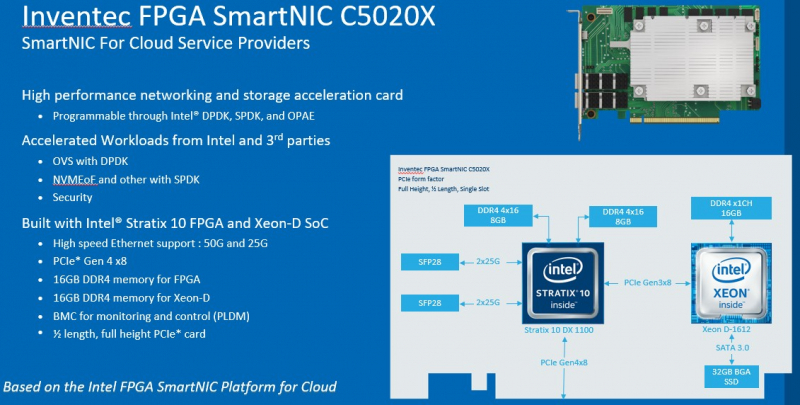

DPU в стиле Intel: сетевые адаптеры с Xeon D, FPGA, HBM и SSDМир сетевых карт становится умнее. Это следующий шаг в дезагрегации ресурсов центров обработки данных. Наличие расширенных возможностей сетевых карт позволяет разгрузить центральный процессор, при этом специализированные сетевые адаптеры обеспечивают более совершенные функции и безопасность. В этой новости мы познакомим вас сразу с двумя адаптерами: Silicom SmartNIC N5010 и Inventec SmartNIC C5020X. Silicom FPGA SmartNIC N5010 предназначена для систем крупных коммуникационных провайдеров. Операторы все чаще стремятся заменить проприетарные форм-факторы от поставщиков телекоммуникационного оборудования на более стандартные варианты. В рамках этого мы видим, что производители ПЛИС не прочи освоить и эту нишу.  В Silicom FPGA SmartNIC N5010 используется Intel Stratix 10 DX с 8 Гбайт памяти HBM. Поскольку пропускная способность памяти становится все большим аспектом производительности системы, HBM будет продолжать распространяться за пределы графических процессоров и FPGA. В SmartNIC и DPU память HBM может использоваться для размещения индексных таблиц поиска и других функций для интенсивных сетевых нагрузок. Помимо HBM SmartNIC N5010 имеет еще 32 Гбайт памяти DDR4 ECC. SmartNIC N5010 потребляет до 225 Вт, что предполагает несколько вариантов исполнения карты, в том числе и с активным охлаждением.  Самая интересная особенность новой карты — 4 сетевых порта по 100 Гбит/с. На плате SmartNIC N5010 установлены две базовые сетевые карты Intel E810 (Columbiaville). На приведенной схеме можно заметить, что используется интерфейс PCIe Gen4 x16, причем их тут сразу два. Для работы четырех 100GbE-портов уже недостаточно одного интерфейса PCIe 4.0 x16. Второй порт PCIe 4.0 x16 может быть подключен через дополнительный кабель к линиям второго процессора, чтобы избежать межпроцессорного взаимодействия для передачи данных.  Вторая новинка, Inventec FPGA SmartNIC C5020X, совмещает на одной плате процессор Intel Xeon D и FPGA Intel Stratix 10. Этот адаптер предназначен для разгрузки центрального процессора в серверах крупных облачных провайдеров. На плате установлен процессор Intel Xeon D-1612 с 32-Гбайт SSD и 16 Гбайт DDR4, подключение к ПЛИС Intel Stratix 10 DX 1100 осуществляется через PCIe 3.0 x8. Нужно отметить, что FPGA Stratix имеет свои собственные 16 Гбайт памяти DDR4, а также обеспечивает сетевые подключения 25/50 Гбит/с и оснащен интерфейсом PCIe 4.0 x8, через который адаптер подключается к хосту.  У Inventec уже есть решение на базе Arm (Inventec X250), которое использует ПЛИС Arria 10 GX660 вместе с сетевым адаптером Broadcom Stingray BCM8804, которое имеет аналогичный форм-фактор и TPD не более 75 Вт. Однако для некоторых организаций наличие единой x86 платформы, включая SmartNIC, упрощает развертывание, поэтому вариант C5020X для таких компаний более предпочтителен. Решение получилось очень интересным, однако вряд ли его можно назвать адаптером для массового рынка, как Intel Columbiaville. На примере этого адаптера Intel показала, что может объединить элементы своего портфеля для создания комплексных решений. Inventec FPGA SmartNIC C5020X является хорошей альтернативой предложению на базе Broadcom, что позволит крупным облачным провайдерам диверсифицировать свои платформы. Несмотря на то, что обе новинки классифицируются как «умные» сетевые адаптеры SmartNIC, вторая, пожалуй, уже ближе к DPU, если сравнивать её с адаптерами NVIDIA DPU, в которых сетевая часть дополнена Arm-процессором и GPU-ускорителем. В данном случае есть и x86-ядра общего назначения, и ускоритель, хотя и на базе ПЛИС. Впрочем, устоявшегося определения DPU и списка критериев соответствия этому классу процессоров пока нет. |

|