Материалы по тегу: dpu

|

29.08.2022 [18:34], Алексей Степин

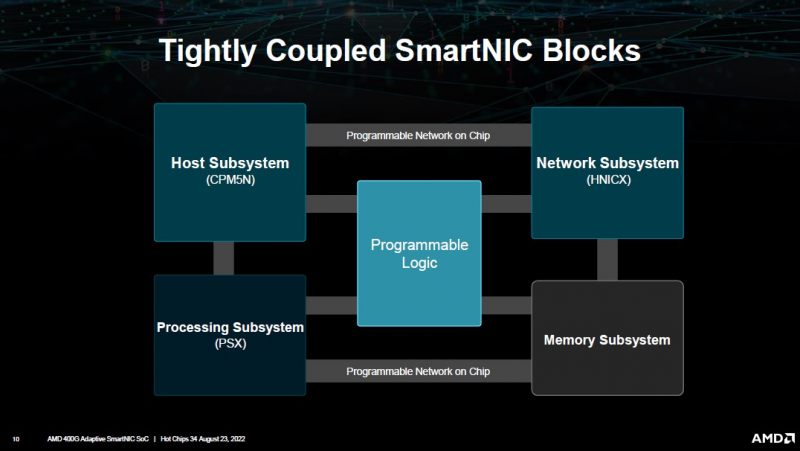

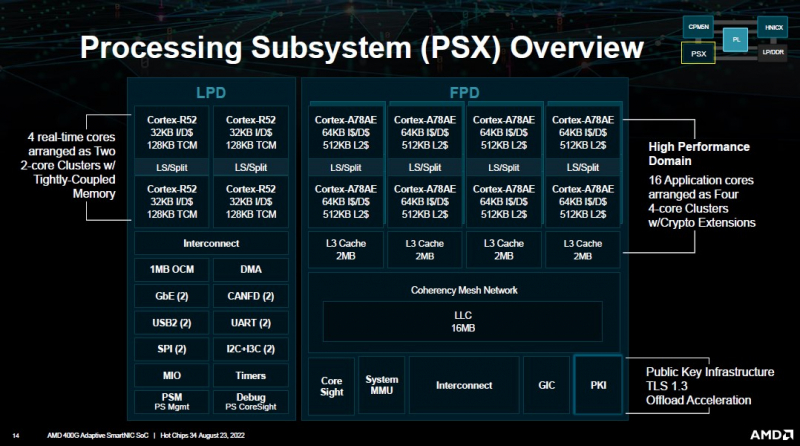

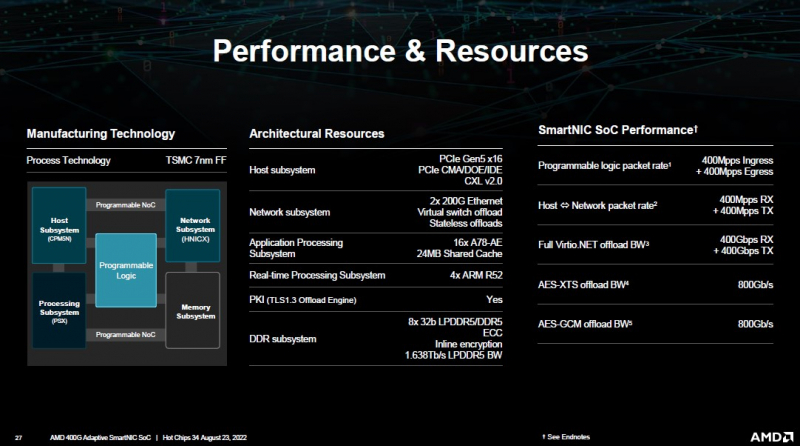

AMD представила DPU-платформу 400G Adaptive Exotic SmartNICНа конференция Hot Chips 34 AMD представила новую платформу 400G Adaptive Exotic SmartNIC. В самой концепции формально нет ничего нового, поскольку DPU уже снискали популярность в среде гиперскейлеров, но вариант AMD сочетает достоинства не двух, а трёх миров: классического ASIC, программируемой логики на базе FPGA и Arm-процессора общего назначения. На деле процессор (PSX) новинки AMD устроен ещё интереснее: он делится на два домена. В первом домене имеется шестнадцать ядер Arm Cortex-A78, организованных в четыре кластера по четыре ядра. Сюда же входят аппаратные движки для ускорения TLS 1.3. Второй домен состоит из четырёх ядер Arm Cortex-R52 и различных контроллеров низкоскоростных шин, таких как UART, USB 2.0, I2C/I3C, SPI, MIO и прочих. Посредством высокоскоростной программируемой внутренней шины блок PSX соединён с другими компонентами: модулем взаимодействия с хост-системой (CPM5N), подсистемой памяти, сетевым модулем HNICX и блоком программируемой логики. CPM5N реализует поддержку PCIe 5.0/CXL 2.0, причём доступен режим работы в качестве корневого (root) комплекса PCIe. Тут же находится настраиваемый DMA-движок. Блок фиксированных сетевых функций представляет собой классический ASIC, обслуживающий пару портов 200GbE. Подсистема памяти представлена 8 каналами DDR5/LPDDR5 с поддержкой 32-бит DDR5-5600 ECC или 160-бит LPDDR5-6400, но говорится и совместимости с другими вариантами памяти, в то числе SCM. Здесь же имеется блок шифрования содержимого памяти с поддержкой стандартов AES-GCM/AES-XTS. 400G Adaptive Exotic SmartNIC имеет развитую поддержку VirtIO и OVS. Также поддерживается виртуализация NVMe-устройств, тоже с шифрованием. Особое внимание AMD уделила тесному взаимодействию всех частей Adaptive Exotic SmartNIC: наличие выделенных линков между блоками хост-контроллера, PSX и FPGA обеспечивает работу на полной скорости в средах, действительно требующих прокачки данных на скоростях в районе 400 Гбит/с. Благодаря наличию FPGA-части 400G новинка можно легко адаптировать к новым требованиям со стороны заказчиков. В частности, решения на базе ПЛИС Xilinx активно поставляются в Китай, где требования к шифрованию существенно отличаются от предъявляемых к аппаратному обеспечению в Европе или США, но наличие блока FPGA позволяет решить эту проблему. У Intel уже есть в сём-то похожая платформа, но более скромная по техническим характеристикам — Oak Springs Canyon (C6000X).

18.08.2022 [17:26], Игорь Осколков

Стартап Pliops получил ещё $100 млн инвестиций и нацелился на североамериканский рынокИзраильская компания Pliops в рамках очередного раунда (D) инвестиций получила $100 млн. В этом раунде к прежним инвесторам примкнули Koch Disruptive Technologies (KDT), SK Hynix, State of Mind Ventures, а также глава Walden International и председатель правления Cadence Лип-Бу Тан (Lip-Bu Tan), недавно присоединившийся к совету директоров Intel. Компания Pliops была основана в 2017 году специалистами в области хранения данных. Впоследствии к стартапу присоединился основатель Mellanox, покинувший последнюю вскоре после того, как она была поглощена NVIDIA. На текущий момент Pliops суммарно получила около $215 млн инвестиций, причём предыдущий раунд ($65 млн) был завершён только в прошлом году. В число инвесторов компании входят AMD, Intel Capital, NVIDIA, SoftBank Ventures Asia, Western Digital и др.

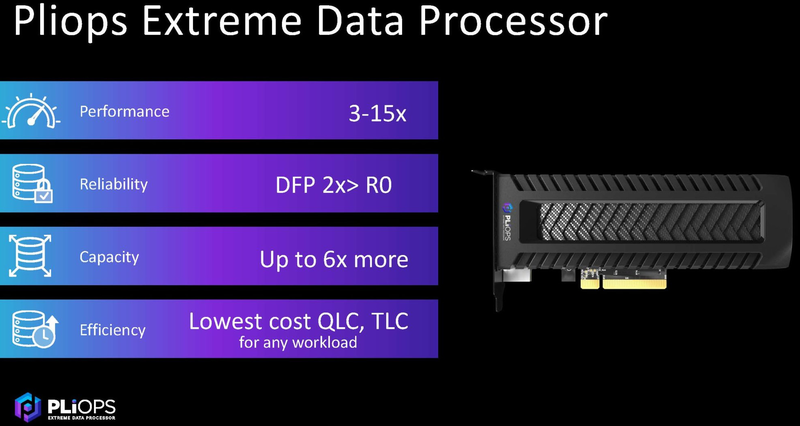

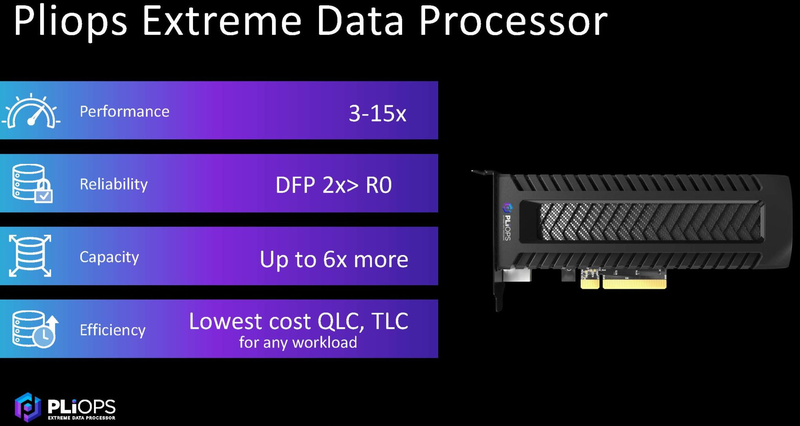

Источник: Pliops Pliops разрабатывает сопроцессоры серии XDP, предназначенные, в частности, для ускорения работы Key-Value СУБД на флеш-массивах. Но в будущем возможности этих DPU будут расширены — решения следующего поколения выйдут уже в 2023 году. Полученные в раунде D средства компания потратит на освоение рынка США. Компания надеется привлечь корпоративных заказчиков, гиперскейлеров и разработчиков HPC-решений. Правда, как сообщает местное издание CTech, в отделе продаж и маркетинга были проведены сокращения персонала.

14.08.2022 [14:50], Владимир Мироненко

SmartNIC будут драйверами роста рынка Ethernet-адаптеров в ближайшие годыСогласно данным исследовательского центра Dell'Oro, SmartNIC будут одним из драйверов роста рынка Ethernet-адаптеров, объём которого, по его прогнозу, достигнет к 2026 году $5 млрд. Скорость подключения продолжит расти и на порты с поддержкой скорости 100 Гбит/с и выше будет приходиться почти половина поставок. В отчёте Dell'Oro «Ethernet Adapter & Smart NIC 5-Year Forecast» за июль 2022 года сообщается, что на SmartNIC будет приходиться растущая доля рынка Ethernet-адаптеров, особенно это относится к гиперескейлерам и сегменту высокопроизводительных приложений. По словам директора по исследованиям Dell'Oro Барона Фунга (Baron Fung), к 2026 году доля SmartNIC составит 38 % всего рынка контроллеров и адаптеров Ethernet. «SmartNIC заменят традиционные сетевые адаптеры для большей части облачной инфраструктуры гиперскейлеров для задач общего назначения и высокопроизводительных рабочих нагрузок», — сказал Фунг, отметив также перспективность использования SmartNIC облачными провайдерами второго эшелона, в корпоративных ЦОД и на телекоммуникационном рынке. SmartNIC позволяют разгрузить хост-систему, переложив на них часть задач, однако они всё ещё дороги, а сети на их основе сложны в реализации. Доходы от продаж SmartNIC, по прогнозам Dell'Oro, будут расти в течение ближайших пяти лет со среднегодовым темпом роста (CAGR) в 21 %, в то время как для традиционных сетевых адаптеров этот показатель составит 5 %. В Dell'Oro также ожидают, что стоимость высокоскоростных портов будет снижаться, поэтому пять лет около 44 % поставок будут приходиться на порты 100GbE+. Так, в США в течение следующих пяти лет в инфраструктуре основных гиперскейлеров — Amazon, Google, Meta✴ и Microsoft — будут преобладать порты 100GbE и 200GbE.

08.08.2022 [20:02], Алексей Степин

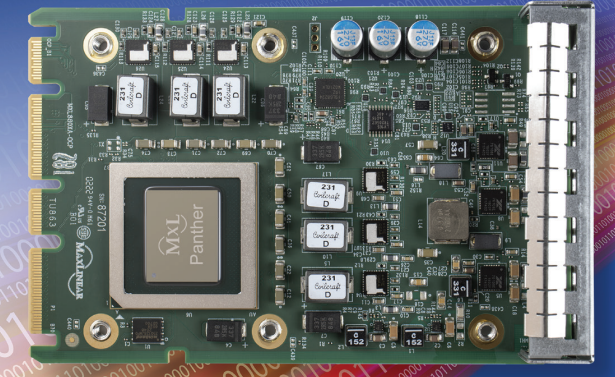

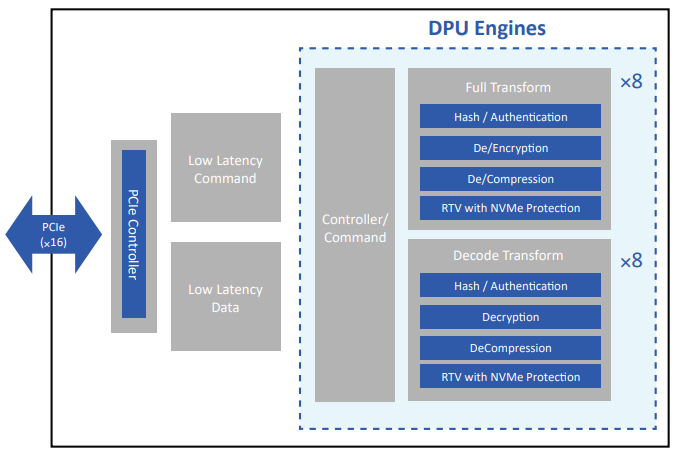

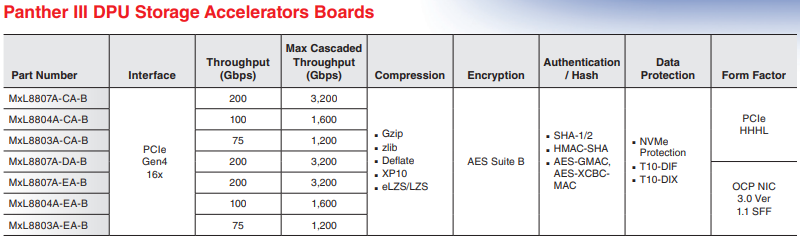

MaxLinear представила DPU Panther IIIНе столь давно концепция сопроцессора данных, DPU, была новинкой, но в 2022 году, пожалуй, уже можно говорить о её вхождении в мейнстрим: подобного рода сопроцессоры представили практически все полупроводниковые гиганты. И на рынке продолжают появляться новые продукты. Так, на конференции Flash Memory Summit 2022 компания MaxLinear представила свой DPU под названием Panther III, который предназначен для ускорения работы с массивами накопителей. Новый чип выполнен с использованием 16-нм техпроцесса и компания-разработчик заявляет о надёжности класса «шесть девяток». Архитектура Panther III включает в себя 16 аппаратных движков-ускорителей для хеширования, (де-)шифрования, (де-)компрессии и сквозной защиты данных (RTV), причём все эти операции делаются за один проход.

Panther III MxL8807A-EA-B. Источник: MaxLinear Последняя функция гарантирует повышенную надёжность, в реальном времени отслеживая правильность выполнения всех операций и корректной работы NVMe-накопителей. Из 16 блоков 8 работают в обе стороны, а другие 8 лишь в одном направлении: расшифровки, декомпрессии и т.д. Фирменная низколатентная архитектура позволяет говорить о задержках в районе 27 мкс при пропускной способности более 200 Гбит/c. При этом новый ускоритель обеспечивает дедупликацию данных вплоть до 12:1.

Архитектура Panther III. Источник: MaxLinear Поддерживается каскадирование нескольких DPU, позволяющее достичь скорости 3200 Гбит/с. Поскольку целью MaxLinear являлось создание недорогого DPU c быстрой интеграцией в существующие системы хранения данных, компания представила сразу несколько вариантов новинки: HHHL PCIe-плата и модуль OCP 3.0. В обоих случаях использован интерфейс PCIe 4.0 x16. При этом в различных вариантах пиковая пропускная способность сопроцессора может составлять 75, 100, либо 200 Гбит/с.

Характеристики ускорителей на базе Panther III. Источник: MaxLinear В комплект поставки входят средства разработчика, API, драйверы и примеры исходного кода. Поддерживаются различные варианты ядра Linux, а также FreeBSD версий 11.х, 12.х и 13.х. В настоящее время доступны образцы модели MxL8807A-EA-B, старшего варианта в исполнении OCP 3.0. Массовые поставки начнутся позднее, но точных сроков и цены компания пока не называет.

26.07.2022 [22:23], Алексей Степин

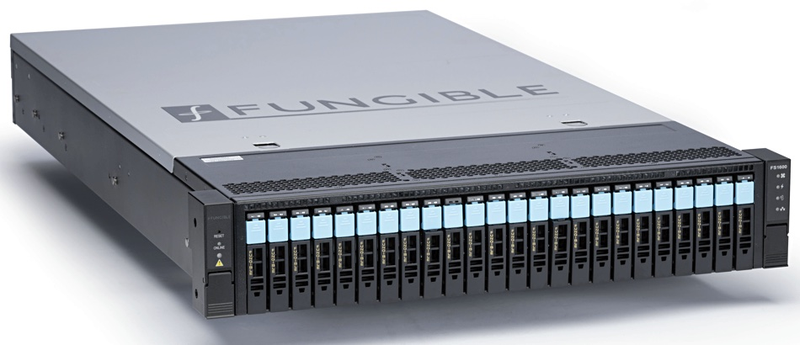

На базе DPU Fungible готовятся «вычислительные» хранилища для СУБДПопулярность «вычислительных накопителей» продолжает расти и эту концепцию сегодня прорабатывают многие, включая таких гигантов, как Samsung. Занимается этой проблемой и компания Fungible, некогда стоявшая у истоков самой концепции DPU. Современную инфраструктуру компания видит составной (composable), работающей под управлением фирменного ПО FunOS и использующим аппаратные ускорители, разработанные Fungible. В настоящее время она тестирует свои DPU в качестве ускорителей операций с базами данных. Во флеш-хранилище F1600 используется чип F1, хост-системы, участвующие в тестах, оснащены ускорителями на базе S1.

Клиенский ускоритель на базе DPU S1. Источник: Fungible Главное в концепции «вычислительных накопителей» — то, что данные, хранящиеся на массиве накопителей, не надо куда-то перемещать для первичной обработки, загружая тем самым интерконнекты всех уровней. Её можно производить прямо на месте. И для этого DPU, разработанные Fungible, подходят как нельзя лучше.

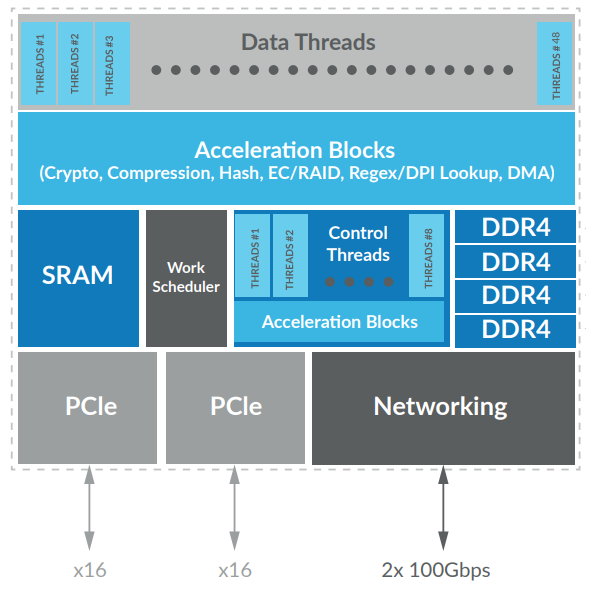

Флеш-хранилище FS1600 содержит DPU F1. Источник: Fungible Флагманский чип F1 содержит 48 ядер MIPS64 с поддержкой мультипоточности SMT4 с аппаратным планировщиком, а также набором движков-ускорителей криптографии, хеширования, поддержки RAID и многих других возможностей. Как сообщает Blocks & Files, перекладывание вычислений на эти движки даёт впечатляющие результаты, в частности, в ускорении обращений к базам данных MySQL.

Архитектура чипов Fungible DPU. Источник: Fungible Даже при однопоточной обработке на DPU время обработки запроса удалось снизить в 75 раз в сравнении с классическим сервером с архитектурой x86. В тесте с использованием регулярных выражений выигрыш составил 27 раз. Сам чип F1 может исполнять 192 потока, но разработчики сомневаются, что целесообразно задействовать их все под одну задачу. Однако даже тестовый прототип показывает отличные результаты. В настоящее время проект «вычислительного хранилища» на базе решений Fungible имеет статус бета-версии, но о нём уже поставлены в известность сообщества Practice and Experience in Advanced Research Computing (PEARC) и OpenInfra Foundation.

08.07.2022 [23:38], Алексей Степин

Ускорители Pliops XDP Extreme прописались в облаке phoenixNAPВ прошлом году компания Pliops представила свой вариант «сопроцессора данных», ускоритель под названием XDP Extreme. Это решение не относится к классу «умных NIC», оно целиком ориентировано на ускорение работы KV-хранилищ с флеш-массивами. А сегодня компания объявила о сотрудничестве с крупным провайдером облачных услуг phoenixNAP. Данный поставщик услуг теперь предлагает bare-metal системы, оснащённые ускорителями XDP Extreme. Развёртывание таких инстансов занимает считанные минуты. Данный DPU позволяет практически полностью устранить все «бутылочные горлышки», связанные с обслуживанием подсистемы хранения данных. В некоторых случаях выигрыш достигает 10x, а в случае сбоя RAID5/6 реконструкция массива проходит в 5 раз быстрее. Кроме того, DPU повышает защищённость хранилища.

Преимущества XDP Extreme. Источник: Pliops Также возросла надёжность использования флеш-накопителей, и даже для QLC заявлено увеличение срока службы: по сравнению с системой без DPU XDP оно может вырасти в некоторых случаях в 7 раз. Использование фирменных API и утилит облегчит управление нагрузками. Новая услуга доступна по модели pay-per-use, с возможностью резервирования на срок от месяца до года.

04.07.2022 [22:25], Алексей Степин

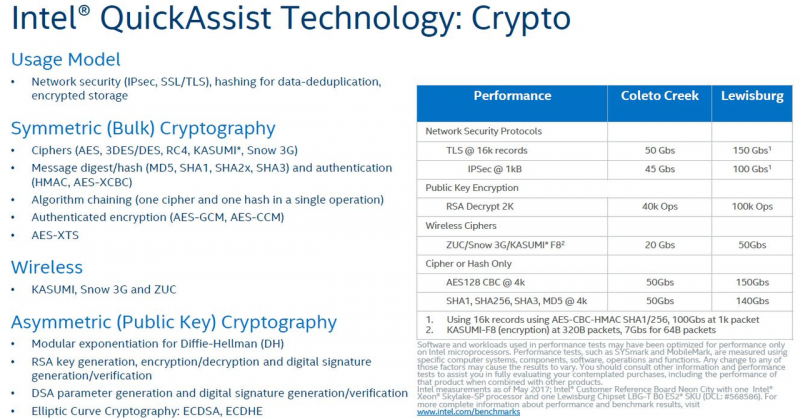

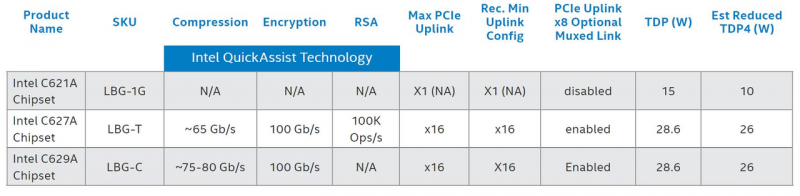

Ускоритель Silicom M20E3ISLB: чипсет Intel Lewisburg в необычном форм-фактореШифрование трафика на высоких скоростях требует достаточно серьёзных вычислительных ресурсов и при отсутствии специфических движков в составе процессора и прочих криптоускорителей способно отъесть немалую долю производительности. Нередко такие движки входят в состав современных процессоров, а ускорители имеют на борту собственный процессор и оперативную память. Но в случае с Silicom M20E3ISLB всё иначе.

Silicom M20E3ISLB. Источник: Silicom Этот ускоритель базируется на технологии Intel QuickAssist, которая в современных реализациях способна работать с протоколами TLS и туннелями IPSec на скоростях 100–150 Гбит/с, и даже в сложных случаях шифрования развивать пропускную способность 50 Гбит/с. Но под радиатором этого ускорителя, выполненного в форм-факторе U.2, скрывается вовсе не ПЛИС, не Arm с собственной памятью и не ASIС, а обычный чипсет Intel С620 (Lewisburg). В процессорах с более высокой степенью интеграции функциональность QAT входит в состав чипа, и, как ни странно, это не флагманские Xeon Scalable, а процессоры серии Atom C2000/C3000/C5000, а также ряд моделей Xeon D, включая D-2100 и D-2700. Но именно в старшей платформе QAT вынесена за пределы процессора. Поэтому большая часть PCIe-ускорителей с поддержкой данной технологии представляют собой чипсет Lewisburg или более ранний Coleto Creek (Intel 8925) с системой питания и интерфейсом PCI Express, в котором они способны работать в режиме Endpoint. Хабы серии Lewisburg не новы, они увидели свет вместе со стартом платформы LGA3647 и процессорами Xeon Scalable с архитектурой Skylake. В младшем варианте C621 криптоускорители отключены, но C627 и обновлённая версия C629 полностью поддерживают QAT и могут работать в режиме x16. Ускоритель Silicom M20E3ISLB ограничен режимом x4, максимальным для формата U.2. Именно по причине QAT тепловыделение этих чипсетов достаточно высоко и достигает почти 30 Вт. Любопытно, что устройство полностью поддерживает режим «горячей замены» и позволяет быстро и просто оснастить практически любой сервер поддержкой ускорения криптографических операций и сжатия/распаковки сетевого трафика на лету. Современные DPU обладают существенно более высокими характеристиками и универсальностью, но решения на базе Lewisburg доступнее, а возможности при этом вполне достаточны для ряда сценариев и скоростей сетевых каналов.

21.06.2022 [23:22], Алексей Степин

Linux Foundation считает, что время DPU пришло: запущен проект Open Programmable InfrastructureНа свет «умные» сетевые адаптеры появились не вчера — технология возмужала и доросла до концепции DPU, сопроцессора данных, могущего взять на себя не только обработку трафика, но и многое другое, вплоть до обслуживания гипервизора. Текущие реализации DPU базируются на проприетарных технологиях, но организация Linux Foundation хочет положить этому конец и сделать такие сопроцессоры по-настоящему популярными. На этой неделе организация объявила о старте инициативы Open Programmable Infrastructure (OPI), целью которой является разработка открытых программных стандартов для DPU, IPU и SmartNIC. Проект уже получил поддержку от многих ведущих разработчиков аппаратного и программного обеспечения, включая NVIDIA, Intel, Marvell, F5, Keysight, Dell Tech и Red Hat. Стоит ожидать дальнейшего увеличения количества участников.

Изображение: opiproject.org За счёт унификации и открытости OPI, считает Linux Foundation, темпы внедрения «умных» сетевых ускорителей существенно вырастут. Для гиперскейлеров и крупных облачных провайдеров проприетарное ПО обычно не проблема, но куда сложнее ситуация выглядит для менее крупных компаний. Проект OPI положит конец ситуации, когда разработчики DPU порой не могут договориться даже о единой терминологии. На первой стадии участники проекта создадут стандартизированные определения для технологий и функций, выполняемых DPU, затем начнётся разработка универсальных API и программных архитектур и фреймворков, не зависящих от «железа» конкретного разработчика. Такой крупный игрок на рынке DPU, как NVIDIA, приветствует инициативу, и в рамках проекта OPI уже открыла доступ к SDK DOCA разработчикам ПО и аппаратных сетевых средств. Компания и ранее обещала сделать DOCA для сетевых ускорителей тем же, чем стал стандарт CUDA для GPU, но теперь, к счастью, стандарт не будет закрытым: библиотеки и прочие средства, а также документация, уже доступны, а открытая лицензия позволит использовать наработки NVIDIA не только для ускорителей BlueField, но и для решений других производителей. Сайт проекта OPI находится здесь, также имеется репозиторий на GitHub.

19.06.2022 [13:32], Алексей Степин

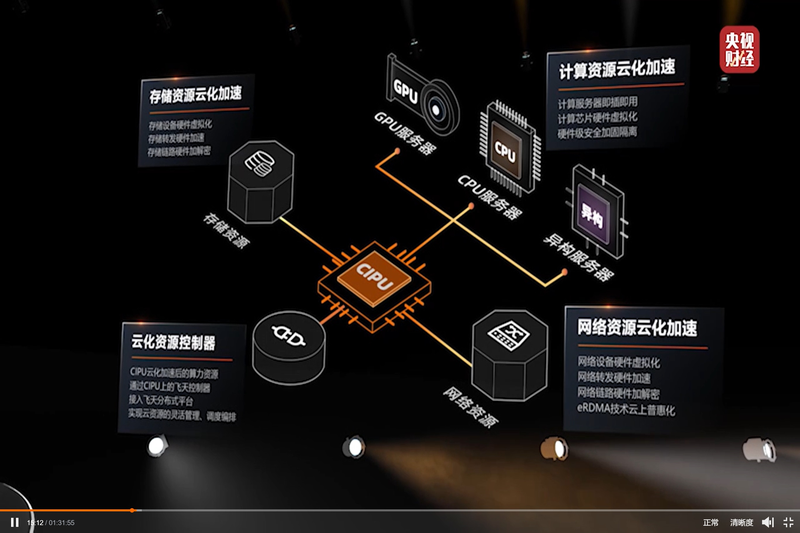

Alibaba Cloud представила свой вариант DPU — Cloud Infrastructure Processing Unit (CIPU)С учётом стремительно наступающей эры DPU/IPU не вызывает удивления, что такой китайский гигант, как Alibaba Cloud, представил своё видение «универсального сетевого сопроцессора», использовав схожий термин Cloud Infrastructure Processing Unit (CIPU). На ежегодном саммите компании Alibaba Cloud анонсировала новый чип, являющийся дальнейшим развитием идей, ранее воплощённых в умном сетевом адаптере X-Dragon, разрабатывавшемся как аналог AWS Nitro. Пока об архитектуре Alibaba CIPU известно не так много, но физически это обычная двухслотовая плата расширения с интерфейсом PCI Express.

Источник: @ogawa_tter Судя по имеющимся данным, в основе лежит четвёртое поколение архитектуры X-Dragon, обеспечившее 20% прирост производительности в сравнении с предыдущим поколением этих процессоров. Что более интересно, в основе новой итерации X-Dragon лежит дуэт технологий Elastic RDMA (eRDMA) и Shared Memory Communications over RDMA (SMC-R). Он позволяет новому ускорителю обращаться к памяти хост-системы напрямую на уровне ядра фирменных ОС Alibaba Cloud Linux 3 и Anolis OS. Для приложений, использующих TCP, всё выглядит прозрачно, но латентность при этом удалось понизить до 5 мкс.

Источник: @ogawa_tter Новые сопроцессоры полностью совместимы со стеком технологий RDMA over Converged Ethernet (RoCE), причём поддерживается даже iWARP, довольно редкий вариант, встречавшийся ранее в адаптерах Intel и Chelsio. Реализации iWARP могут быть сложнее RoCE, т.к. используют многослойную архитектуру и ряд твиков, а в итоге нередко показывают менее высокую производительность. Но благодаря поддержке обеих технологий новое решение Alibaba получилось поистине универсальным.

Источник: @ogawa_tter Результаты тестов весьма обнадёживают: в частности, для Redis ускорители CIPU за счёт SMC-R позволили поднять количество обрабатываемых запросов на 50%, а в сценариях с данными, чувствительными к латентности, прирост составил 20%. Исходя из опубликованных в японском блоге Tadashi Ogawa, это действительно полноценный IPU, могущий стать мостом между сетью, подсистемами хранения данных, CPU, GPU и прочими ускорителями. Компания активно развивает собственную аппаратную инфраструктуру и в прошлом году уже представила 128-ядерный 5-нм процессор Yitian 710 на базе набора инструкций Armv9 c 8 каналами DDR5, поддержкой PCIe 5.0 (96 линий) и при этом способный работать на частотах до 3,2 ГГц.

10.06.2022 [23:31], Алексей Степин

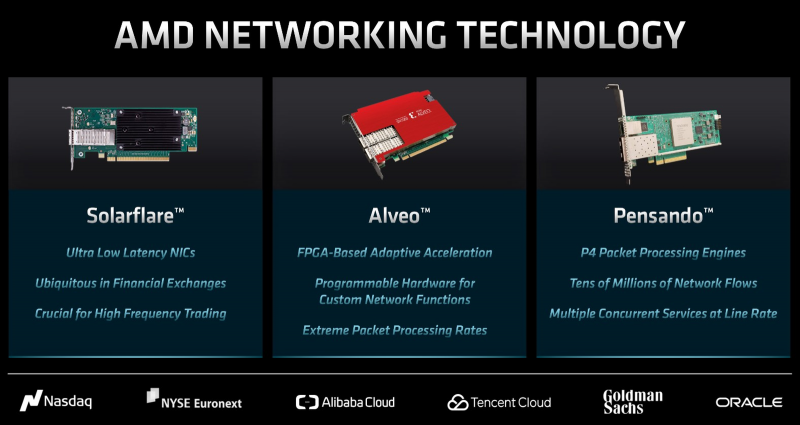

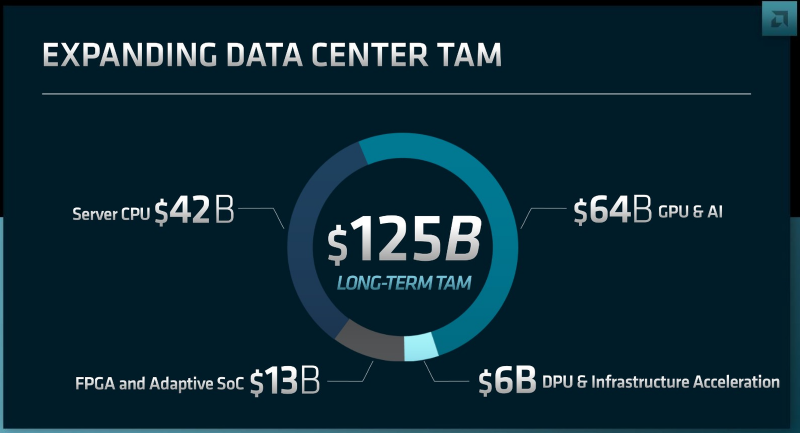

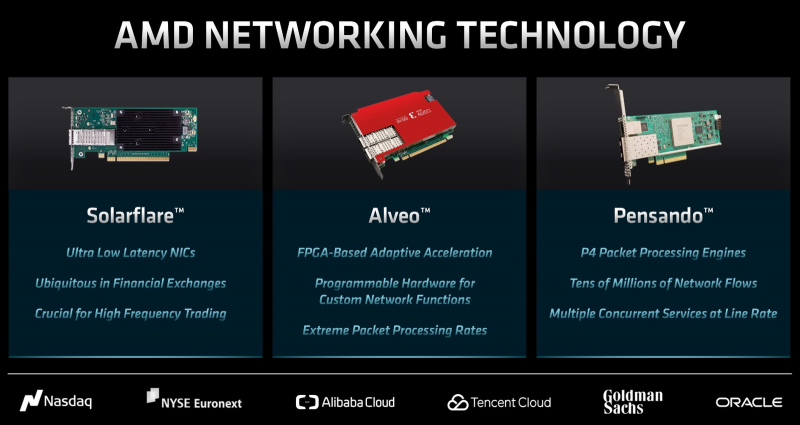

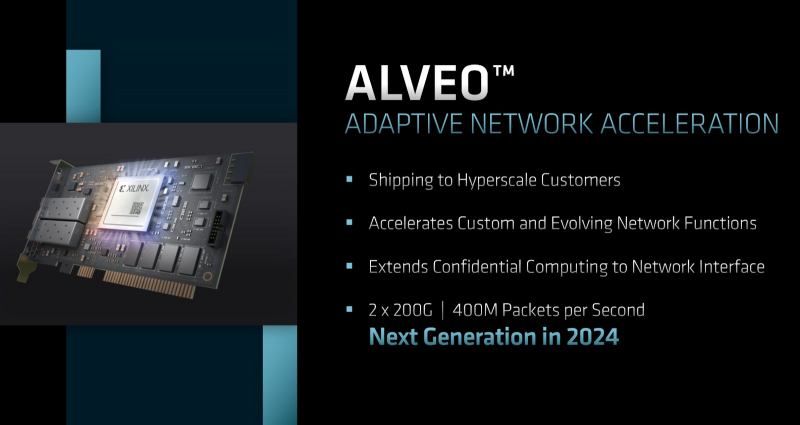

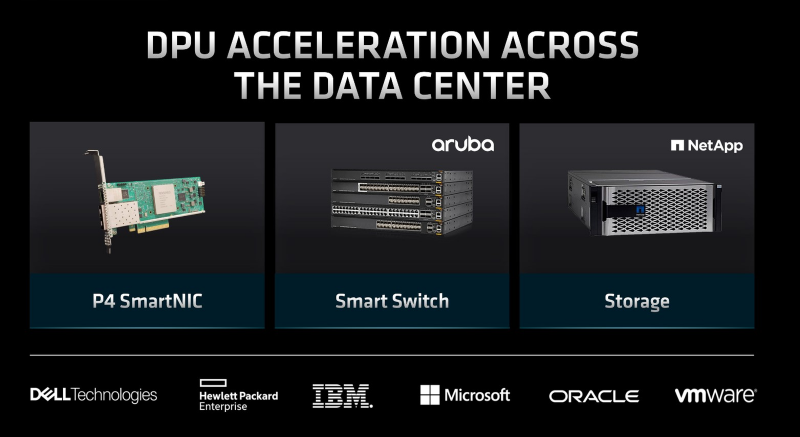

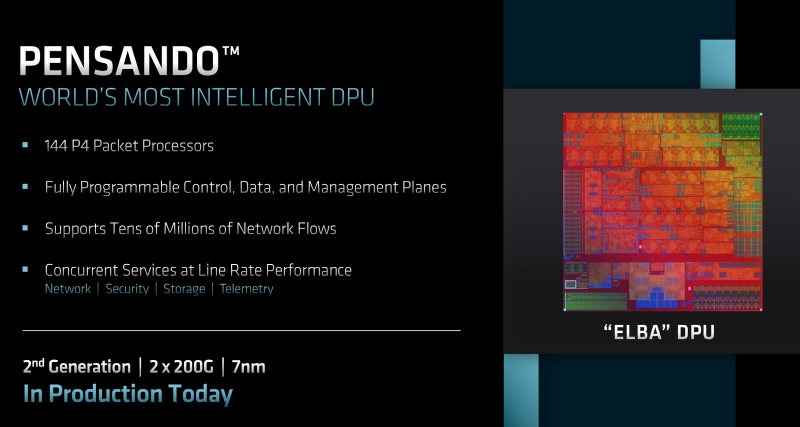

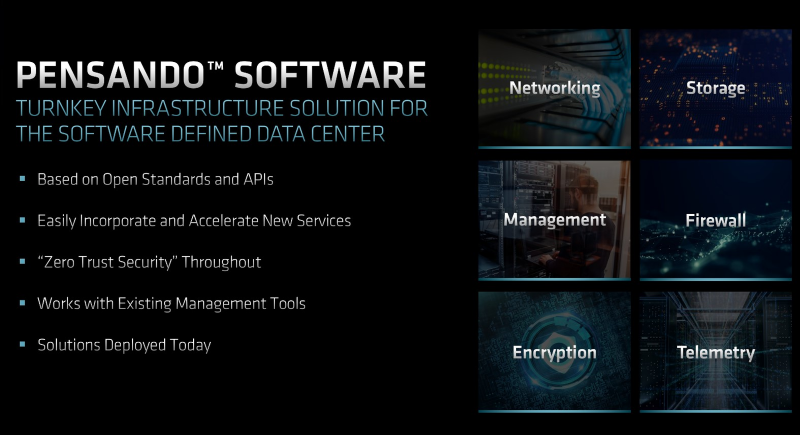

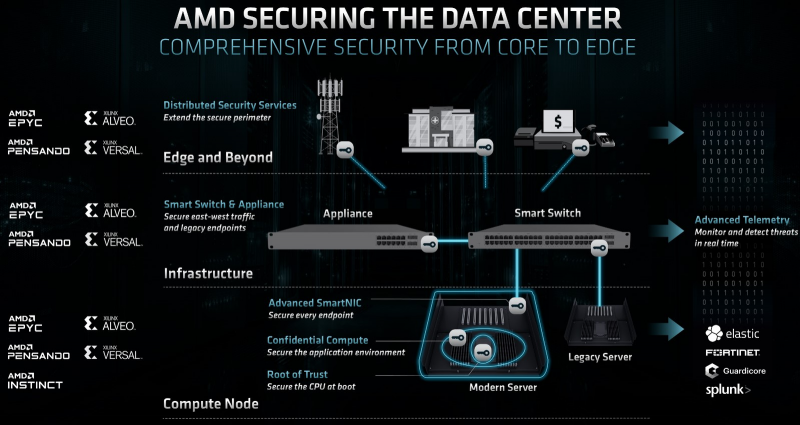

Решения Xilinx и Pensando помогут AMD завоевать рынок ЦОДО грядущих серверных APU MI300, сочетающих архитектуры Zen 4 и CDNA 3, и сразу нескольких сериях процессоров EPYC мы уже рассказали, но на мероприятии Financial Analyst Day 2022 компания поделилась и другими планами относительно серверного рынка, которые весьма обширны. Они включают в себя использование разработок и технологий Xilinx и Pensando. Фактически AMD теперь владеет полным портфолио аппаратных решений для ЦОД и рынка HPC: процессорами EPYC, ускорителями Instinct, SmartNIC и DPU на базе чипов Xilinx и Pensando и, наконец, FPGA всё той же Xilinx. Долгосрочные перспективы рынка ЦОД AMD оценивает в $125 млрд, из них на долю ускорителей приходится $64 млрд, а классические процессоры занимают лишь второе место с $42 млрд; остальное приходится на DPU, SmartNIC и FPGA. Теперь у AMD есть полный спектр «умных» сетевых решений практически для любой задачи, включая сценарии, требующие сверхнизкой латентности. Эту роль берут на себя адаптеры Solarflare. Более универсальные ускорители Xilix Alveo обеспечат поддержку кастомных сетевых функций и блоков ускорения, а также высокую производительность обработки пакетов. Ускорители могут быть перепрограммированы, что потенциально позволит существенно оптимизировать затраты на сетевую инфраструктуру крупных ЦОД. Гиперскейлерам они уже поставляются, в текущем виде они имеют до двух 200GbE-портов и совокупную скорость обработки до 400 млн пакетов в секунду. Следующее поколение должно увидеть свет в 2024 году, здесь AMD придерживается двухгодичного цикла. Выпускается и 7-нм DPU Pensando Elba, также предоставляющий пару 200GbE-портов. В отличие от Alveo, это более узкоспециализированное устройство, содержащее 144 P4-программируемых пакетных движка. Помимо них имеются выделенные аппаратные движки ускорения криптографии и сжатия/декомпрессии данных. Уникальный программно-аппаратный стек Pensando, унаследованный AMD, обеспечивает ряд интересных возможностей, востребованных в крупных системах виртуализации на базе ПО VMware — например, полноценную поддержку виртуализации NVMe, поддержку NVMe-oF/RDMA, в том числе и NVMe/TCP, а также полноценное шифрование и туннели IPSec на полной линейной скорости 100 Гбит/с с временем отклика 3 мкс и джиттером в районе 35 нс. Разработки Pensando уже используются такими крупными поставщиками сетевого оборудования и СХД, как Aruba (коммутаторы с DPU) и NetApp (системы хранения данных). Таким образом, AMD вполне вправе говорить о том, что современный высокопроизводительный ЦОД может быть целиком построен на базе технологий компании, от процессоров и ускорителей до интерконнекта и специфических акселераторов. Поддержка доверенных вычислений, включая полное шифрование содержимого памяти делает такие ЦОД и более безопасными, что немаловажно в современном мире, полном кибер-угроз. В том же направлении движутся NVIDIA BlueField и Intel IPU, а также целый ряд других игроков. |

|