Материалы по тегу: soc

|

10.04.2024 [00:31], Николай Хижняк

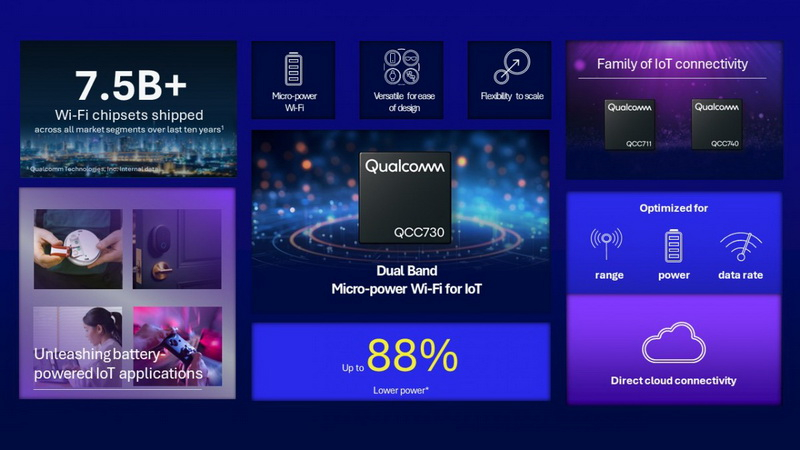

Qualcomm представила энергоэффективный Wi-Fi чип для IoT и платформу RB3 Gen 2 для роботовQualcomm представила двухдиапазонный Wi-Fi чип QCC730, обеспечивающий улучшенную дальность работы и скорость передачи данных при сниженном потреблении энергии. Новинка предназначена для устройств интернета вещей (IoT). Qualcomm заявляет для него уменьшение энергопотребления на 88 % по сравнению с решением предыдущего поколения. Новый Wi-Fi-чип предлагает прямое подключение к облаку, интеграцию с Matter, открытый SDK а также возможность разгрузки подключения к облаку через программный стек. Он представлен как альтернатива Bluetooth для IoT-приложений и может функционировать в том числе в хост-режиме. Впрочем, возможности QCC730 весьма скромны, хотя и достаточны для IoT. Он предлагает поддержку Wi-Fi 4 (802.11a/b/g/n) в конфигурации 1×1 с шириной канала 20 МГц и канальной скоростью менее 30 Мбит/с (MCS3). «Сердцем» SoC является ядро Cortex-M4F.

Источник изображений: Qualcomm Помимо QCC730 компания Qualcomm также представила ИИ-платформу для роботов RB3 Gen 2 корпоративного и промышленного назначения. В состав платформы входит процессор Qualcomm QCS6490 (8 ядер с частотой до 2,7 ГГц) с графическим ядром Adreno 643. Для неё заявляется поддержка нескольких датчиков камеры, а также наличие встроенного модуля Wi-Fi 6E. Кроме того, RB3 Gen 2 предлагает поддержку Bluetooth 5.2 и LE-аудио. Платформа RB3 Gen 2 предназначена для широкого спектра продуктов, включая дроны, камеры и другие промышленные устройства. Комплекты для разработчиков включают блок питания, динамики, USB-кабель и плату. Qualcomm также предлагает Vision Kits с монтажными кронштейнами и камерами CSI. Для заинтересованных клиентов платформа Qualcomm RB3 Gen 2 станет доступна в июне этого года.

23.02.2024 [19:06], Сергей Карасёв

Meta✴ ищет в Индии и США специалистов для разработки ИИ-ускорителей и SoC для дата-центровКомпания Meta✴, по сообщению The Register, опубликовала множество объявлений о поиске специалистов для разработки интегральных схем специального назначения (ASIC). Речь идёт о создании собственных ускорителей для машинного обучения и ИИ, а также SoC для дата-центров. Сейчас для ИИ-задач Meta✴ массово применяет решения NVIDIA. Кроме того, компания присматривается к ускорителям AMD Instinct MI300. С целью снижения зависимости от сторонних поставщиков и сокращения расходов Meta✴ также проектирует собственные аппаратные компоненты. В частности, весной прошлого года Meta✴ анонсировала свой первый кастомизированный процессор, разработанный специально для ИИ-нагрузок. Изделие под названием MTIA v1 (Meta✴ Training and Inference Accelerator) представляет собой ASIC в виде набора блоков, функционирующих параллельно. Задействованы 64 вычислительных элемента в виде матрицы 8 × 8, каждый из которых объединяет два ядра RISC-V. Кроме того, компания создала чип MSVP (Meta✴ Scalable Video Processor) для обработки видеоматериалов. В разработке также находятся собственные ИИ-ускорители Artemis.

Источник изображения: Meta✴ Как теперь сообщается, Meta✴ ищет ASIC-инженеров с опытом работы в области архитектуры, дизайна и тестирования. Необходимы специалисты в Бангалоре (Индия) и Саннивейле (Калифорния, США). В некоторых вакансиях работодателем указана собственно Мета✴, тогда как в других случаях указан Facebook✴. От кандидатов в числе прочего требуется «глубокий опыт в одной или нескольких ключевых сферах, связанных с созданием сложных SoC для дата-центров». Тестировщикам необходимо иметь опыт проверки проектов для ЦОД, связанных с машинным обучением, сетевыми технологиями и пр. Некоторые вакансии были впервые опубликованы в соцсети LinkedIn в конце декабря 2023 года и обновлены в феврале нынешнего года. Претендентам обещаны неплохие зарплаты. Для каких именно задач компании Meta✴ требуются аппаратные решения, не уточняется. Но сетевые источники отмечают, что это может быть инференс, создание новых ИИ-платформ и т.п.

09.02.2024 [23:02], Алексей Степин

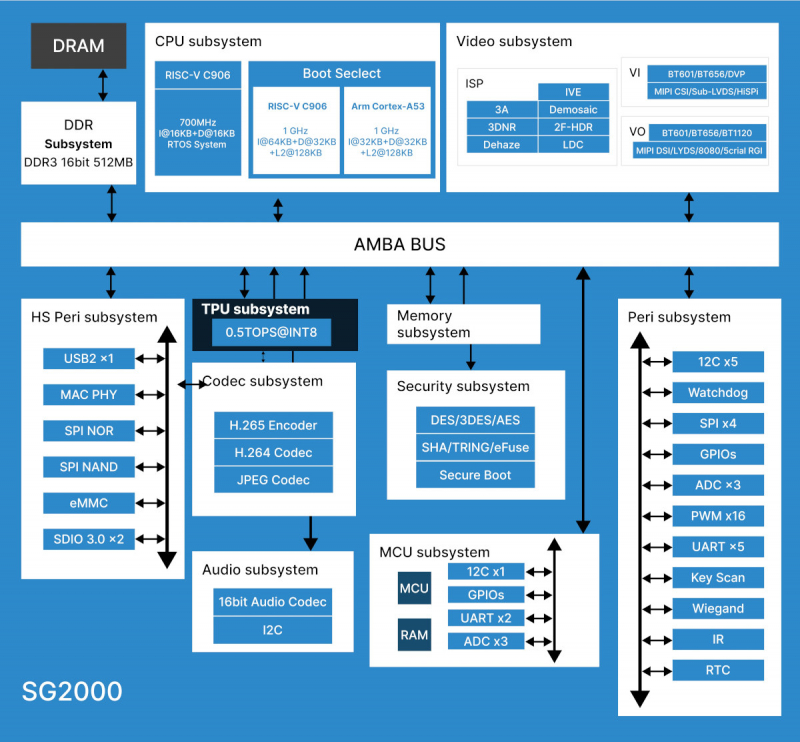

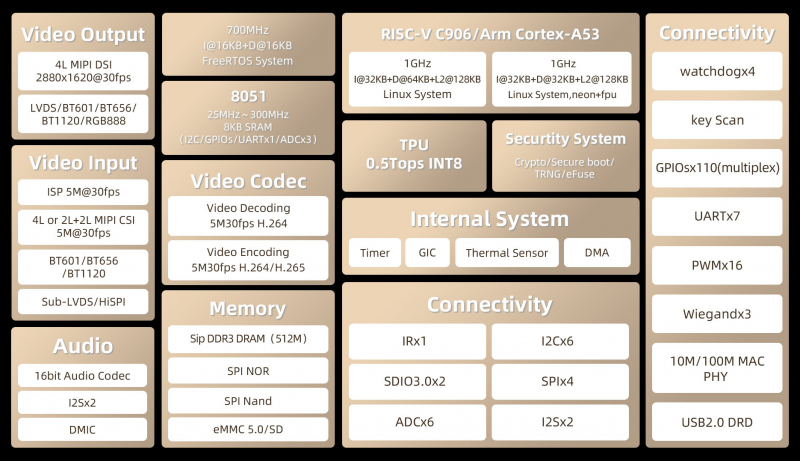

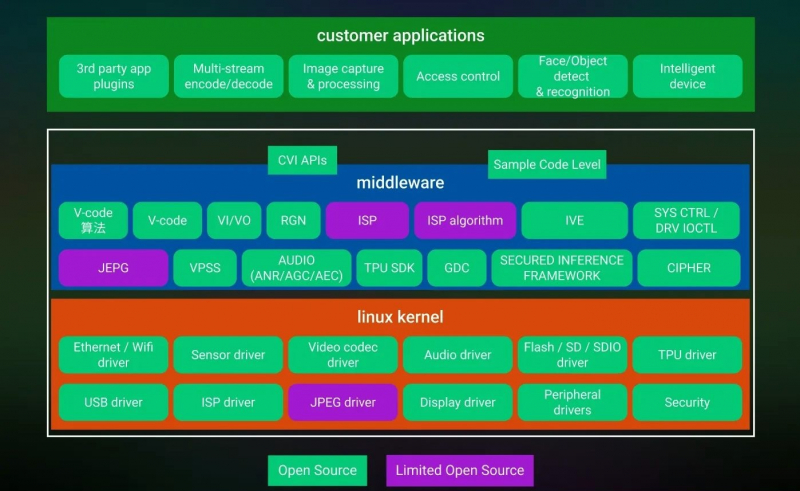

Sophgo представила гибридные SoC, сочетающие ядра Arm и RISC-VКомпания Sophgo, китайский разработчик тензорных нейрочипов и процессоров с архитектурой RISC-V, анонсировала универсальные SoC SG2000 и SG2002. Они способны работать с несколькими операционными системами одновременно, в частности, Linux, Android и FreeRTOS. Для этого разработчики снабдили новинку процессорными ядрами разных типов — RISC-V, Arm Cortex-A, Intel 8051, а также отдельным ИИ-сопроцессором. Решения предназначены для «умного интернета вещей» (Artificial Intelligence of Things, AIoT), включая «умные» IP-камеры и контроллеры систем умного дома. При этом микросхемы очень компактны, корпуса LFBGA имеют габариты всего 10 × 10 × 1,3 мм с 205 контактами. Они способны работать в диапазоне температур 0-70 °C. Архитектура новых процессоров Sophgo действительно необычна: в состав входят два 64-битных ядра RISC-V C906 с частотами 1000 и 700 МГц, одно ядро Arm Cortex-A53 с частотой 1000 МГц, а также ядро контроллера 8051 с варьирующейся от 25 до 300 МГц частотой; последнее используется для задач реального времени и имеет собственный небольшой объём SRAM. Графического ускорителя в составе новых SoC нет, однако средства обработки видеопотока имеются: блок VPU поддерживает кодирование и декодирование в форматах H.264/H.265 с разрешением 5К@30. Интегрированный NPU для работы с INT8 имеет мощность 0,5 Топс у SG2000 и 1 Топс у SG2002. Объём интегрированной оперативной памяти составляет 512 или 256 Мбайт. Подключение дисплеев реализовано через интерфейс MIPI DSI, поддерживаются разрешения вплоть до 2880 × 1620@30, имеется четыре линии MIPI CSI для подключения модулей видеокамер. Также предусмотрен 16-битный аудиокодек с двумя шинами I2S и микрофонным входом DMIC. Есть контроллеры 100 Мбит/с Ethernet и USB 2.0. Широко представлены интерфейсы для подключения различной низкоскоростной периферии: 5 × UART, 4 × SPI, 16 × PWM, 1 × IR, 6 × I2C, 6 × ADC и до 128 линий GPIO. Не забыты средства безопасности: чипы имеют собственные криптоблоки с аппаратными генераторами случайных чисел, поддерживают безопасную загрузку и располагают комплектом «пережигаемых предохранителей» (e-fuse). Разработчик заявляет о поддержке SDK на базе Linux 5.10, однако на момент анонса программные компоненты ещё не были полностью доступны. Если верить опубликованным слайдам, SDK планируется весьма развитое, включая поддержку Arduino-сред для одного из ядер RISC-V (с частотой 700 МГц). На базе новых чипов анонсировано сразу три одноплатных решения: Shenzhen MilkV Technology Duo S (SG2000) и Duo 256M (SG2002), а также Sipeed LicheeRV Nano (SG2002). Последний вариант уже доступен на Aliexpress, к нему также имеется первичная документация и репозиторий на GitHub.

10.01.2024 [19:40], Сергей Карасёв

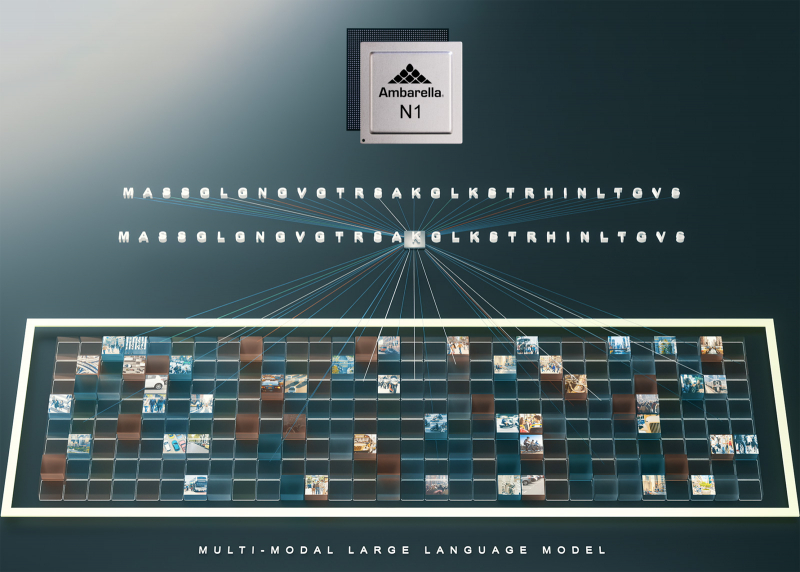

Новые чипы Ambarella привнесут возможности генеративного ИИ в периферийные устройстваКомпания Ambarella сообщила о том, что её SoC обеспечат поддержку генеративного ИИ на периферии. Ожидается, что это позволит расширить возможности множества систем и приложений, включая робототехнику и средства видеоаналитики. Отмечается, что по сравнению с ускорителями на базе GPU и другими специализированными решениями, чипы Ambarella представляют собой полноценные «системы на чипе», которые обеспечивают до трёх раз более высокую энергоэффективность на каждый токен. Изначально Ambarella обеспечит оптимизированные возможности генеративного ИИ на своих SoC среднего и высокого классов. Это, в частности, изделие CV72 для устройств с энергопотреблением до 5 Вт. Кроме того, функции генеративного ИИ будут поддерживать чипы новой серии N1 с «производительностью серверного уровня» при энергопотреблении до 50 Вт. Чипы N1 основаны на архитектуре Ambarella CV3-HD, изначально разработанной для приложений автономного вождения. Утверждается, что изделие N1 способно обрабатывать модель Llama2-13B с выводом до 25 токенов в секунду в однопоточном режиме при потребляемой мощности менее 50 Вт. Все изделия Ambarella используют новую платформу для разработчиков Cooper. Чтобы ускорить вывод конечных продуктов на рынок, Ambarella предварительно портировала и оптимизировала популярные большие языковые модели, такие как Llama-2 и LLava.

04.12.2023 [13:22], Сергей Карасёв

MediaTek представила чипы M60 и T300 для IoT-устройств 5G RedCapКомпания MediaTek анонсировала аппаратные решения с поддержкой 5G RedCap — модем M60 и чипсеты серии T300. Эти изделия предназначены для создания IoT-устройств коммерческого и промышленного классов с пониженным энергопотреблением и продолжительным сроком работы от батареи. 5G RedCap, или Reduced Capability, снижает требования к устройствам и в то же время предоставляет расширенные возможности по сравнению с 4G: это повышенная скорость передачи данных и уменьшенные задержки. При этом в отличие от обычных инфраструктур 5G, сети RedCap предоставляют базовые возможности подключения, адаптированные для менее мощного и требовательного IoT-оборудования. Модем M60 и чипсеты T300 соответствуют стандарту 3GPP R17. Благодаря фирменной технологии MediaTek UltraSave 4.0, по заявлениям MediaTek, изделие M60 обеспечивает снижение энергопотребления до 70 % по сравнению с аналогичными решениями 5G eMBB (enhanced Mobile BroadBand) и до 75 % по сравнению с решениями 4G. Как утверждается, T300 — это первая в мире 6-нм однокристальная радиочастотная система (RFSOC) для сетей RedCap. Она содержит одно ядро Arm Cortex-A35. Заявленная скорость загрузки данных через мобильную сеть достигает 227 Мбит/с, скорость передачи в сторону базовой станции — 122 Мбит/с. Изготавливаться изделие будет на предприятии TSMC. Появление изделий MediaTek 5G RedCap, как отмечается, поможет разработчикам в создании энергоэффективных, надёжных и экономичных IoT-продуктов нового поколения для потребительского, корпоративного и промышленного секторов. Устройства на базе MediaTek T300 будут представлены в I половине 2024-го, а коммерческие образцы выйдут во II полугодии.

30.06.2023 [11:10], Сергей Карасёв

China Mobile создала два телеком-чипа с архитектурой RISC-VКомпания China Mobile, по сообщению ресурса DigiTimes, представила два чипа собственной разработки с архитектурой RISC-V, которые предназначены для использования в телекоммуникационном оборудовании, а также в устройствах для Интернета вещей (IoT). В частности, анонсировано первое в мире изделие RISC-V категории LTE Cat.1 — решение с обозначением CM8610 LTE-Cat.1. Данный стандарт предусматривает максимальную скорость загрузки информации на уровне 10,3 Мбит/с и скорость передачи данных в сторону базовой станции до 5,2 Мбит/с. Кроме того, компания China Mobile разработала чип CM6620 NB-IoT на базе RISC-V для узкополосного Интернета вещей. На базе данного стандарта формируются сети для передачи данных с многочисленных устройств: это могут быть всевозможные автономные датчики, счётчики, трекеры и пр.

Источник изображения: pixabay.com Сообщается также, что China Mobile создала микроядерную операционную систему OneOS для сегмента IoT. Утверждается, что автономность кода этой платформы достигает 100 %. Обеспечиваются высокие показатели надёжности и безопасности. ОС может применяться в оборудовании для умного дома и транспорта, а также в промышленных устройствах. Наконец, China Mobile представила первый полностью интеллектуальный протокол подключения для оборудования IoT, направленный на решение проблем взаимодействия и межплатформенного обмена данными.

25.04.2023 [18:42], Сергей Карасёв

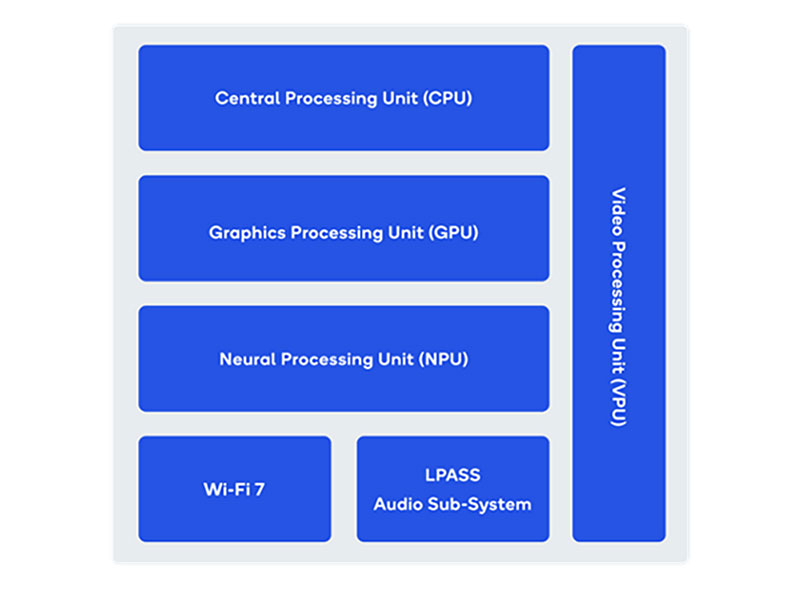

Qualcomm представила четыре новых SoC для IoT-устройствКомпания Qualcomm анонсировала сразу четыре SoC для различного IoT-оборудования — дронов, устройств для облачных игр, мобильных гаджетов и пр. Изделия, представленные в ходе отраслевой выставки Hannover Messe 2023, получили обозначения QCS8550, QCM8550, QCS4490 и QCM4490. Первые два из дебютировавших чипов — это мощные модели, единственное различие между которыми заключается в том, что вариант «М» имеет встроенный сотовый модем. Они изготавливаются по 4-нм технологии. Конфигурация включает одно ядро Kryo GoldPlus (3,2 ГГц), четыре ядра Gold (2,8 ГГц) и три ядра Silver (2,0 ГГц). Возможно использование оперативной памяти LPDDR5/5x-4200.

Источник изображения: Qualcomm В состав SoC входят блок Adreno 740 GPU, приёмник GPS/GLONASS/BeiDou/Galileo/QZSS/NavIC, адаптеры Wi-Fi 7 (802.11be) и Bluetooth 5.3, модуль сенсоров Qualcomm Sensing Hub 3.0, NPU-блок Qualcomm Hexagon Tensor Processor (HTP) и пр. Поддерживается фотосъёмка с разрешением до 200 МПикс. Чип QCM8550 наделён модемом 5G. Возможно декодирование видеоматериалов 4K240/8K60. Новинки подходят для таких сфер применения, как автономные мобильные роботы, промышленные дроны, ИИ-устройства и др. В свою очередь, QCS4490 и QCM4490 оптимизированы для мобильных Android-гаджетов. Они получили два ядра Gold A78 (2,4 ГГц) и шесть ядер Silver A55 (2,0 ГГц), ускоритель Adreno GPU 613, контроллер памяти LPDDR4X/LPDDR5, адаптеры Wi-Fi 6E и Bluetooth 5.2 и поддержку GPS/BeiDou/GLONASS/Galileo/NavIC. В состав QCM4490 включён модем 5G.

19.10.2022 [16:54], Сергей Карасёв

MaxLinear представила чипы MxL31712 и MxL31708 для сетевых устройств с Wi-Fi 7Компания MaxLinear анонсировала первые, по её словам, в отрасли одночиповые SoC с поддержкой Wi-Fi 7. Изделия с обозначениями MxL31712 и MxL31708 найдут применение в шлюзах, маршрутизаторах, точках доступа, повторителях, оборудовании для беспроводных mesh-сетей и других устройствах. Высокоинтегрированные чипы выполнены в соответствии со спецификацией IEEE 802.11be (Extremely High Throughput, EHT). Обеспечивается обратная совместимость со стандартами IEEE 802.11a/b/g/n/ac/ax. По сравнению с Wi-Fi 6 достигается увеличение пропускной способности более чем 70 %.

Источник изображения: MaxLinear Говорится о поддержке каналов шириной 320 МГц, модуляции 4096 QAM, технологии MLO и MRU, DPD и AFC, on-the-fly MAC, а также интерфейса PCIe 4.0. Предусмотрена выделенная антенна Zero Wait DFS (ZWDFS). Возможно сосуществование с PAN-сетями. Трёхдиапазонный чип MxL31712 поддерживает до 12 пространственных потоков, а пропускная способность (PHY) заявлена на уровне 18,6 Гбит/с. Изделие ориентировано на оборудование премиального сегмента. Двухдиапазонное решение MxL31708 поддерживает до восьми пространственных потоков и пропускную способность до 17 Гбит/с. Этот чип рассчитан в том числе на устройства среднего уровня. Новые изделия могут использоваться в связке с решениями серии AnyWAN для ШПД-оборудования. Это, в частности, SoC URX850, URX851 и MxL25641, о которых можно узнать в нашем материале.

18.10.2022 [19:00], Сергей Карасёв

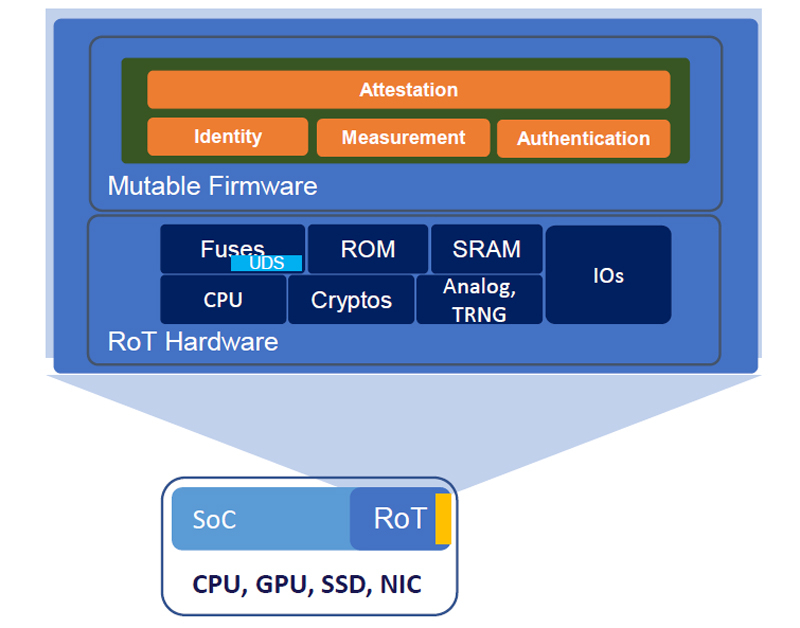

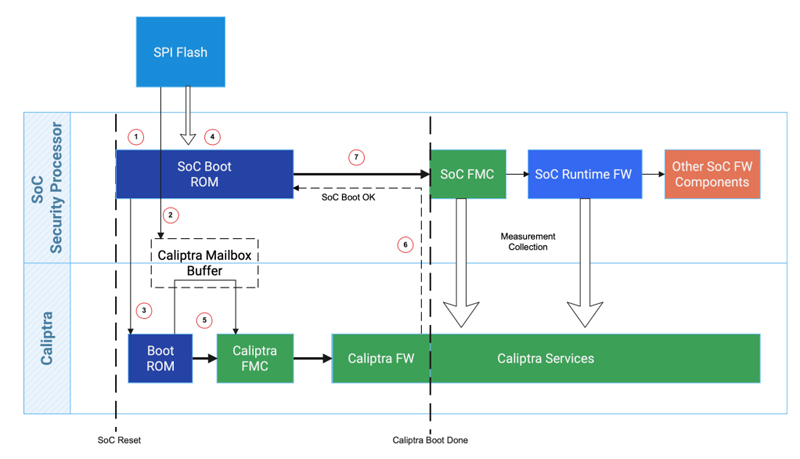

AMD, Google, Microsoft и NVIDIA представили Caliptra — проект по повышению безопасности каждого чипаВ ходе саммита OCP (Open Compute Project) анонсирована открытая спецификация Caliptra 0.5, призванная повысить безопасность процессоров, ускорителей, накопителей и практически любых систем-на-чипе (SoC). Речь идёт об аппаратной реализации технологии Root of Trust (RoT). Она предназначена для проверки целостности и подлинности прошивок и другого встроенного, а также системного программного обеспечения.  RoT гарантирует, что только доверенное ПО может исполняться на чипе. Отмечается, что традиционно средства RoT отделены от SoC и обычно обеспечиваются материнской платой. Однако новые бизнес-модели, предполагающие периферийные и облачные вычисления, предъявляют повышенные требования к обеспечению безопасности. Спецификация Caliptra 0.5 как раз и решает данную проблему.

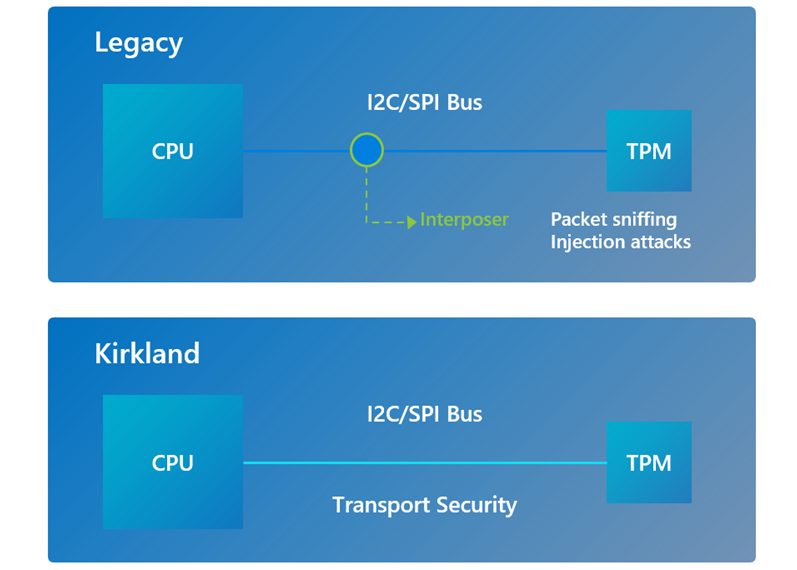

Источник изображений: Caliptra В разработке решения приняли участие AMD, Google, Microsoft и NVIDIA. Спецификация будет поддерживаться различными аппаратными изделиями следующего поколения — CPU, GPU, SSD, NIC и иные ASIC. Отмечается, что Caliptra 0.5 RTL (IP-блоки на базе RISC-V с необходимой обвязкой) распространяется через CHIPS Alliance (Common Hardware for Interfaces, Processors and Systems) — консорциум, который работает над созданием целого спектра открытых решений для SoC и высокоплотных упаковок чипов.  «Существует потребность в улучшенной прозрачности и согласованности низкоуровневой аппаратной безопасности. Мы открываем исходный код Caliptra вместе с нашими партнёрами для удовлетворения этих потребностей», — отмечает Microsoft. Также компания совместно с Google, Infineon и Intel представила Project Kirkland, направленный на создание защищённого канала связи между CPU и TPM с использованием программных средств.

Источник: Microsoft Спецификация Caliptra 0.5 доступна здесь для оценки. На основе отзывов будет выработан окончательный стандарт, отвечающий различным потребностям в зависимости от варианта использования. Кроме того, доступен исходный код, что поможет членам сообщества интегрировать решение в свои микросхемы. Говорится также, что выход спецификации знаменует собой важный шаг вперёд в сторону общеотраслевого сотрудничества в области информационной безопасности.

10.09.2022 [13:53], Сергей Карасёв

Представлены чипы AnyWAN с ядрами Intel Atom, выпущенные не IntelКомпания MaxLinear сообщила о доступности трёх «систем на чипе» (SoC) серии AnyWAN для ШПД-оборудования — клиентских маршрутизаторов и шлюзов. Дебютировали изделия URX850, URX851 и MxL25641. Новинки используют ядра Intel Atom, что неудивительно — соответствующее подразделение по разработке клиентских сетевых решений MaxLinear выкупила у Intel два года назад. AnyWAN URX850/URX851 (FCBGA-837, 24 × 26 мм) предназначены для устройств класса 10 Гбит/с. Они объединяют четыре ядра Atom с тактовой частотой до 2,0 ГГц. Поддерживается использование до 16 Гбайт (L)PDDR4 и флеш-накопителей eMMC 5.1. Набор интерфейсов таков: XFI WAN, 4 × PCIe 3.0, 4 × XFI/PCIe 4.0, 4 × 2.5 GbE PHY и 2 × USB 3.2. Для URX851 также заявлена поддержка 10 Гбит/с PON MAC. Число линий HSIO равно девяти у URX850 и восьми у URX851. Среди прочего упомянуты интерфейсы Voice DSP и PCM/SPI для FXS и DECT.

Источник изображения: MaxLinear Изделие AnyWAN MxL25641 (FCBGA-577, 17 × 17 мм) ориентировано на оборудование класса 5 Гбит/с. Задействованы два ядра Atom с тактовой частотой до 1,7 ГГц. Можно использовать до 4 Гбайт памяти (L)PDDR4 и флеш-накопитель eMMC 5.1. Набор интерфейсов включает 10 Гбит/с PON MAC, XFI WAN, 4 × PCIe 3.0, 4 × XFI/PCIe 4.0, 2 × USB 3.2 и 9 × HSIO. Для разработчиков будут доступны комплекты AnyWAN Hardware Development Kit URX851 и AnyWAN Hardware Development Kit MxL25641. |

|