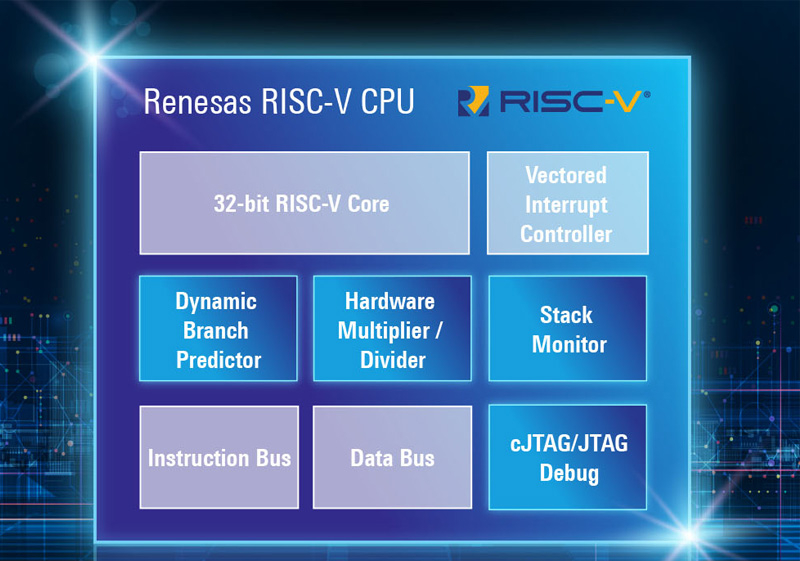

Компания Renesas Electronics объявила о создании собственного 32-битного процессорного ядра на основе архитектуры набора команд RISC-V (ISA) с открытым исходным кодом. Решение дополнит существующее семейство 32-бит микроконтроллеров (MCU) Renesas, включая проприетарные изделия RX и RA на архитектуре Arm Cortex-M.

RISC-V-ядро Renesas предназначено для создания чипов общего назначения. Предполагается, что такие процессоры найдут применение в устройствах Интернета вещей, потребительской электронике, медицинском оборудовании, индустриальных системах и пр.

Источник изображения: Renesas

Новое ядро может выполнять функции основного контроллера приложений или дополнительного вторичного узла в SoC. Кроме того, ядро подходит для применения в составе внутрикристальных подсистем и специализированных изделий (ASSP). Производительность оценивается в 3,27 CoreMark/МГц, что, как утверждает Renesas, превосходит показатель других сопоставимых по классу решений, представленных на рынке.

В ядре Renesas реализованы некоторые расширения RISC-V ISA: это M (целочисленное умножение/деление), А (атомарные операции с памятью), С (сжатый формат команд; подмножество RV32I) и В (инструкции для манипуляций с битами). Компания Renesas планирует выпустить свой первый MCU на базе RISC-V и соответствующие инструменты разработки в I квартале 2024 года. Тогда же будут обнародованы технические подробности о продукте.

Источник: