Материалы по тегу: epi

|

16.05.2024 [01:05], Игорь Осколков

И для ИИ, и для HPC: первые европейские серверные Arm-процессоры SiPearl Rhea1 получат HBM-памятьКомпания SiPearl уточнила спецификации разрабатываемых ею серверных Arm-процессоров Rhea1, которые будут использоваться, в частности, в составе первого европейского экзафлопсного суперкомпьютера JUPITER, хотя основными чипами в этой системе будут всё же гибридные ускорители NVIDIA GH200. Заодно SiPearl снова сдвинула сроки выхода Rhea1 — изначально первые образцы планировалось представить ещё в 2022 году, а теперь компания говорит уже о 2025-м. При этом существенно дизайн процессоров не поменялся. Они получат 80 ядер Arm Neoverse V1 (Zeus), представленных ещё весной 2020 года. Каждому ядру полагается два SIMD-блока SVE-256, которые поддерживают, в частности, работу с BF16. Объём LLC составляет 160 Мбайт. В качестве внутренней шины используется Neoverse CMN-700. Для связи с внешним миром имеются 104 линии PCIe 5.0: шесть x16 + две x4. О поддержке многочиповых конфигураций прямо ничего не говорится. Очень похоже на то, что SiPearl от референсов Arm особо и не отдалялась, поскольку Rhea1 хоть и получит четыре стека памяти HBM, но это будет HBM2e от Samsung. При этом для DDR5 отведено всего четыре канала с поддержкой 2DPC, а сам процессор ожидаемо может быть поделён на четыре NUMA-домена. И в такой конфигурации к общей эффективности работы с памятью могут быть вопросы. Именно наличие HBM позволяет говорить SiPearl о возможности обслуживать и HPC-, и ИИ-нагрузки (инференс). На примере Intel Xeon Max (Sapphire Rapids c 64 Гбайт HBM2e) видно, что наличие сверхбыстрой памяти на борту даёт прирост производительности в означенных задачах, хотя и не всегда. Однако это другая архитектура, другой набор инструкций (AMX), другая же подсистема памяти и вообще пока что единичный случай. С Fujitsu A64FX сравнения тоже не выйдет — это кастомный, дорогой и сложный процессор, который, впрочем, доказал эффективность и в HPC-, и даже в ИИ-нагрузках (с оговорками). В MONAKA, следующем поколении процессоров, Fujitsu вернётся к более традиционному дизайну. Пожалуй, единственный похожий на Rhea1 чип — это индийский 5-нм C-DAC AUM, который тоже базируется на Neoverse V1, но предлагает уже 96 ядер (48+48, два чиплета), восемь каналов DDR5 и до 96 Гбайт HBM3 в четырёх стеках, а также поддержку двухсокетных конфигураций. AWS Graviton3E, который тоже ориентирован на HPC/ИИ-нагрузки, вообще обходится 64 ядрами Zeus и восемью каналами DDR5. Наконец, NVIDIA Grace и Grace Hopper в процессорной части тоже как-то обходятся интегрированной LPDRR5x, да и ядра у них уже Neoverse V2 (Demeter), и своя шина для масштабирования имеется. В любом случае в 2025 году Rhea1 будет выглядеть несколько устаревшим чипом. Но в этом же году SiPearl собирается представить более современные чипы Rhea2 и обещает, что их разработка будет не столь долгой как Rhea1. Компанию им должны составить европейские ускорители EPAC, тоже подзадержавшиеся. А пока Европа будет обходиться преимущественно американскими HPC-технологиями, от которых стремится рано или поздно избавиться.

10.03.2024 [22:13], Сергей Карасёв

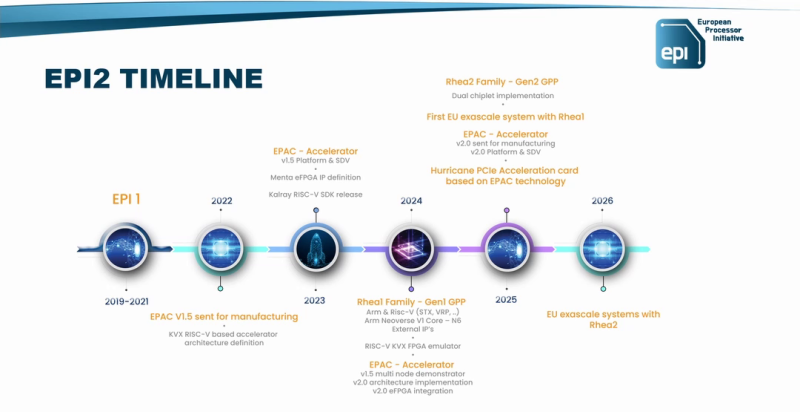

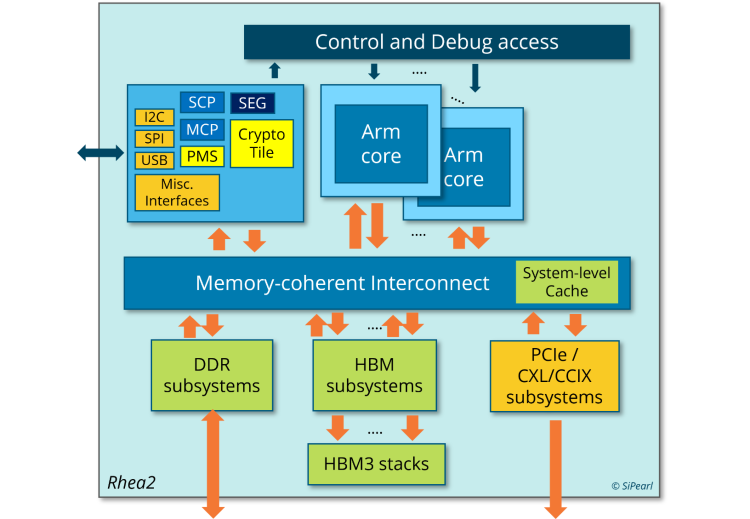

Arm-процессор SiPearl Rhea2 для европейских суперкомпьютеров выйдет в 2025 годуКонсорциум European Processor Initiative (EPI) раскрыл планы по выпуску HPC-процессоров нового поколения с архитектурой Arm. Речь идёт о чипах Rhea2, которые, как ожидается, войдут в состав следующего европейского суперкомпьютера экзафлопсного уровня. Разработчиком изделий Rhea является французская компания SiPearl. Процессор первого поколения на базе Arm Neoverse V1 обладает высокой энергетической эффективностью. Он производится на предприятии TSMC с использованием 6-нм технологии N6. Чип станет основой одного из блоков экзафлопсного суперкомпьютера Jupiter, который в нынешнем году будет запущен в Юлихском исследовательском центре (FZJ) в Германии. О процессоре Rhea2 информации пока не слишком много. Известно, что он получит двухчиплетную компоновку. Ожидается, что будет реализована поддержка памяти HBM и DDR5. Разработчик переведёт Rhea2 на более «тонкий» по сравнению с чипом первого поколения техпроцесс. Сообщается, что Rhea2 дебютирует в 2025 году. Процессор будет задействован в новом европейском НРС-комплексе — вероятно, в системе «Жюль Верн» (Jules Vernes), которая расположится во Франции. Ввод этого суперкомпьютера в эксплуатацию запланирован на 2026 год. Создание машины финансируется Евросоюзом, Францией и Нидерландами, а её управление возьмёт на себя Французское национальное агентство по высокопроизводительным вычислениям (GENCI), которое на 49 % принадлежит французскому правительству. Генеральный директор SiPearl Филипп Ноттон (Philippe Notton) отметил, что разработка чипа Rhea2 проходит быстрее, поскольку компания многому научилась при создании изделия первого поколения и учла допущенные ошибки. Он добавил, что SiPearl сотрудничает со многими партнёрами, включая NVIDIA, AMD и Intel, но вдаваться в подробности о характеристиках Rhea2 не стал. Эксперты полагают, что Rhea2 будет использовать ядра Neoverse 3 (Poseidon).

04.03.2024 [17:00], Руслан Авдеев

Евросоюз намерен добиться полупроводникового суверенитета, используя архитектуру RISC-VВ Евросоюзе активно инвестируют в инициативы, призванные обеспечить полупроводниковый суверенитет благодаря использованию открытой архитектуры RISC-V. EE Times сообщает, что инициативу курирует Барселонский суперкомпьютерный центр (Barcelona Supercomputing Center или BSC) — пионер в разработке европейских решений RISC-V. Страны ЕС беспокоит полупроводниковая зависимость от иностранных компаний, и это беспокойство усугубляется относительно недавним дефицитом чипов в мире. В то же время за использование в своих решениях архитектуры RISC-V никому не надо платить и ни у кого не нужно получать разрешений на её применение, поэтому технология так привлекательна для разработчиков. BSC представляет собой один из ведущих исследовательских центров Европы. Он играет ключевую роль в разработке чипов на архитектуре RISC-V и возглавляет несколько проектов, связанных с этой технологией, в частности, European Processor Initiative (EPI). В рамках инициативы EPI стоимостью €70 млн разрабатывается новое поколение высокопроизводительных процессоров. Связанная с BSC компания OpenChip должна найти коммерческое применение разработанным технологиям. BSC начал создавать собственные чипы семейства Lagarto довольно давно — первые 65-нм варианты представили ещё в мае 2019 года. Сегодня речь идёт уже о четвёртом поколении, которое будет выпускаться в соответствии с 7-нм техпроцессом. Центр работает и с другими европейскими компаниями и исследовательскими организациями над созданием комплексной экосистемы RISC-V, включающей ПО, ОС и компиляторы. Подобные инициативы должны снизить зависимость Евросоюза от американских и азиатских производителей — отсутствие в ЕС зрелой индустрии высокопроизводительных чипов расценивается как значимая уязвимость. Европа считает, что RISC-V — идеальная платформа для достижения суверенитета, при этом бесплатная. Впрочем, эксперты признают, что о полной независимости не может быть речи из-за сложности экосистемы полупроводниковой индустрии. Но у Европы есть большая база знаний и потенциал разработки новых решений, предпринимаются и шаги к организации производства. В BSC уже экспериментировали с Arm-процессорами, но после Brexit и приобретения компании Arm группой Softbank, выяснилось, что собственной региональной технологии у ЕС нет, тогда и обратили внимание на общедоступную RISC-V. В 2019 году Еврокомиссию убедили в необходимости начать выпуск чипов на этой архитектуре для суперкомпьютеров. В числе других европейских компаний, предлагающих RISC-V продукты, есть Gaiser, Esperanto Technologies, Semidynamics и Codasip, но они уделяют больше внимания процессорам и ускорителям, а не конечным готовые решения. По оценкам экспертов, в Евросоюзе компаний, работающих с RISC-V, пока недостаточно. Тем не менее, организаторы новых инициатив предостерегают от нереалистичных ожиданий и призывают к стратегическому сотрудничеству — для производства требуются не только разработки, но и сырьё, высокоточное оборудование, и др. Европа может рассчитывать на выпуск решений в пределах 7-нм, более современные техпроцессы пока слишком дороги. Впрочем, ЕС уже добился значительного прогресса в достижении полупроводникового суверенитета с помощью RISC-V.

22.09.2021 [21:16], Алексей Степин

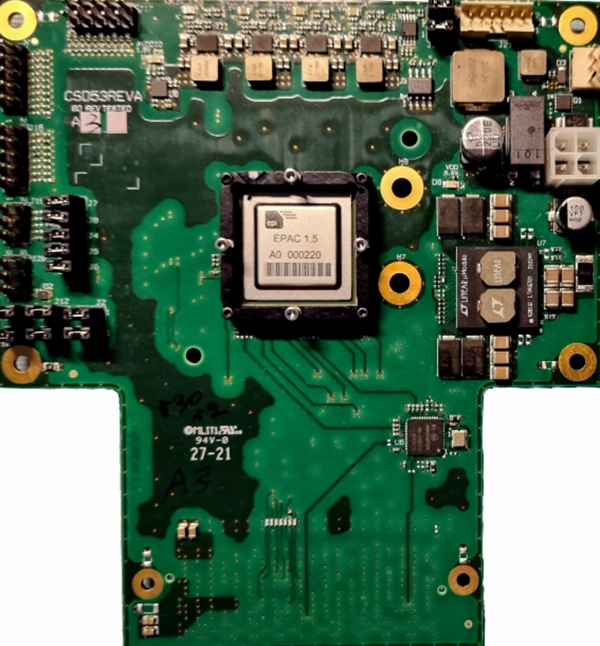

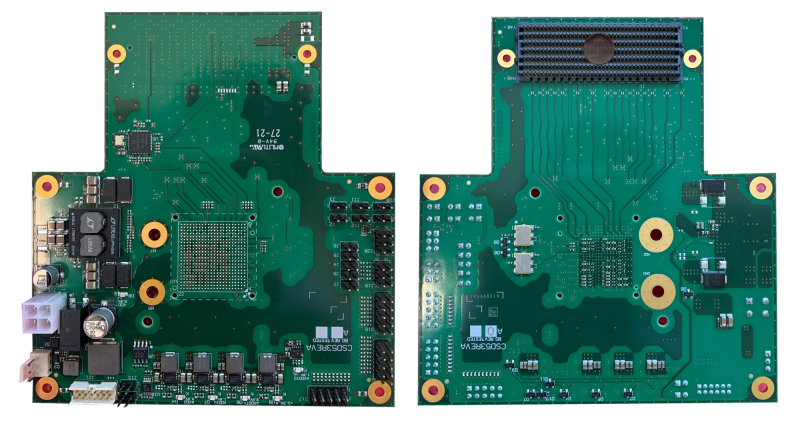

Выпущена тестовая партия европейских высокопроизводительных RISC-V процессоров EPI EPAC1.0Наличие собственных высокопроизводительных процессоров и сопровождающей их технической инфраструктуры — в современном мире вопрос стратегического значения для любой силы, претендующей на первые роли. Консорциум European Processor Initiative (EPI), в течение долгого времени работавший над созданием мощных процессоров для нужд Евросоюза, наконец-то, получил первые весомые плоды. О проекте EPI мы неоднократно рассказывали читателям в 2019 и 2020 годах. В частности, в 2020 году к консорциуму по разработке мощных европейских процессоров для систем экза-класса присоединилась SiPearl. Но сегодня достигнута первая серьёзная веха: EPI, насчитывающий на данный момент 28 членов из 10 европейских стран, наконец-то получил первую партию тестовых образцов процессоров EPAC1.0.

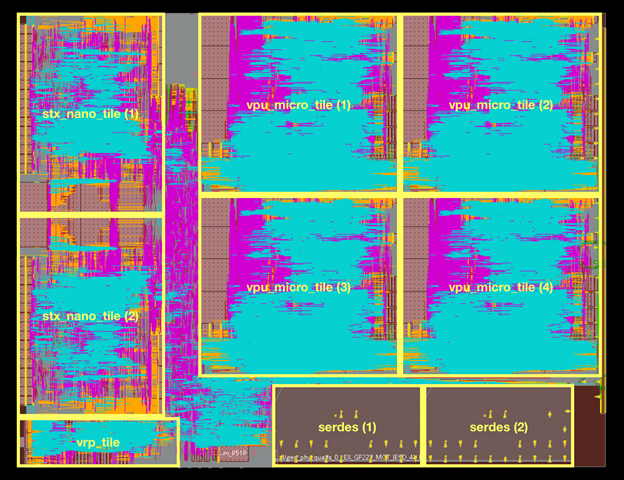

Источник изображений: European Processor Initiative (EPI) По предварительным данным, первичные тесты новых чипов прошли успешно. Процессоры EPAC имеют гибридную архитектуру: в качестве базовых вычислительных ядер общего назначения в них используются ядра Avispado с архитектурой RISC-V, разработанные компанией SemiDynamics. Они объединены в микро-тайлы по четыре ядра и дополнены блоком векторных вычислений (VPU), созданным совместно Барселонским Суперкомпьютерным Центром (Испания) и Университетом Загреба (Хорватия).

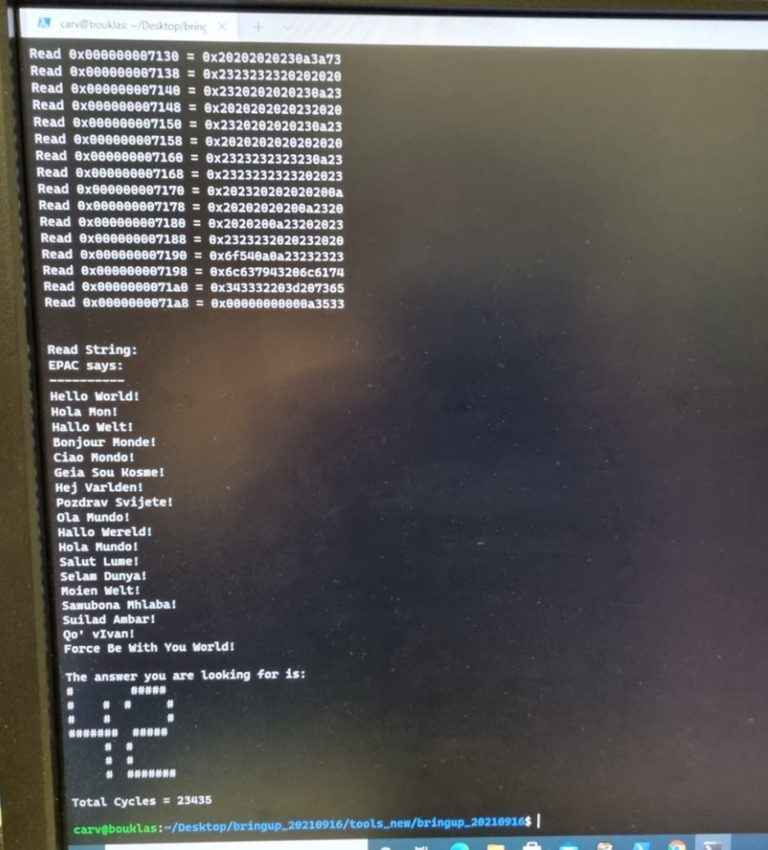

Строение кристалла EPAC1.0 Каждый такой тайл содержит блоки Home Node (интерконнект) с кешем L2, обеспечивающие когерентную работу подсистем памяти. Имеется в составе EPAC1.0 и описанный нами ранее тензорно-стенсильный ускоритель STX, к созданию которого приложил руку небезызвестный Институт Фраунгофера (Fraunhofer IIS). Дополняет картину блок вычислений с изменяемой точностью (VRP), за его создание отвечала французская лаборатория CEA-LIST. Все ускорители в составе нового процессора связаны высокоскоростной сетью, использующей SerDes-блоки от EXTOLL.  Первые 143 экземпляра EPAC произведены на мощностях GlobalFoundries с использованием 22-нм техпроцесса FDX22 и имеют площадь ядра 27 мм2. Используется упаковка FCBGA 22x22. Тактовая частота невысока, она составляет всего 1 ГГц. Отчасти это следствие использования не самого тонкого техпроцесса, а отчасти обусловлено тестовым статусом первых процессоров. Но новорожденный CPU жизнеспособен: он успешно запустил первые написанные для него программы, в числе прочего, ответив традиционным «42» на главный вопрос жизни и вселенной. Ожидается, что следующее поколение EPAC будет производиться с использованием 12-нм техпроцесса и получит чиплетную компоновку. |

|