Материалы по тегу: turin

|

18.12.2023 [13:18], Сергей Карасёв

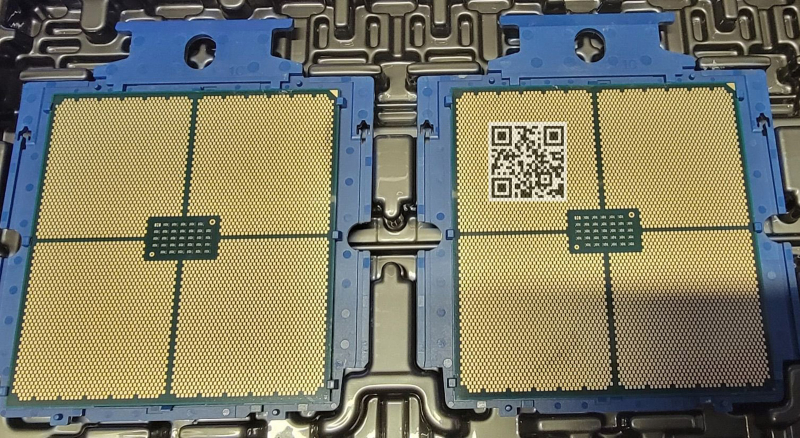

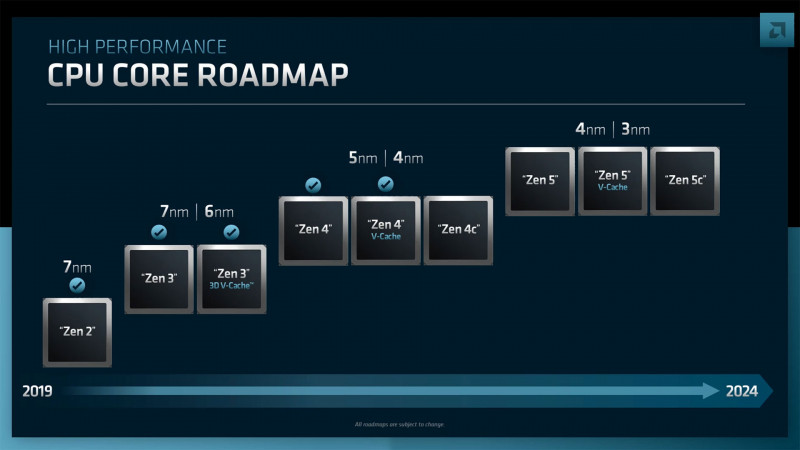

Процессор AMD EPYC Turin показался на «живых» фото: до 192 ядер Zen5cСетевые источники, по сообщению ресурса VideoCardz, обнародовали «живые» фотографии и новые данные о процессорах AMD EPYC пятого поколения с кодовым именем Turin (EPYC 7005). Эти чипы ориентированы на серверы для дата-центров и облачных платформ. О разработке процессоров EPYC Turin компания AMD говорила ещё в начале лета 2022 года. Тогда отмечалось, что будут доступны три разновидности кристаллов: обычные (Zen 5), с 3D V-Cache и «облачные» (Zen 5c) с высокой плотностью. Ожидается, что на коммерческом рынке изделия появятся до конца 2024 года.

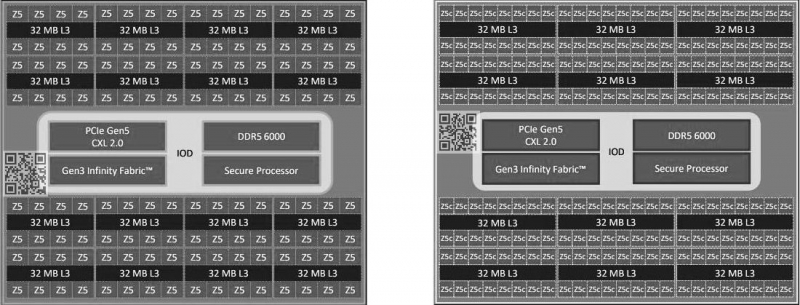

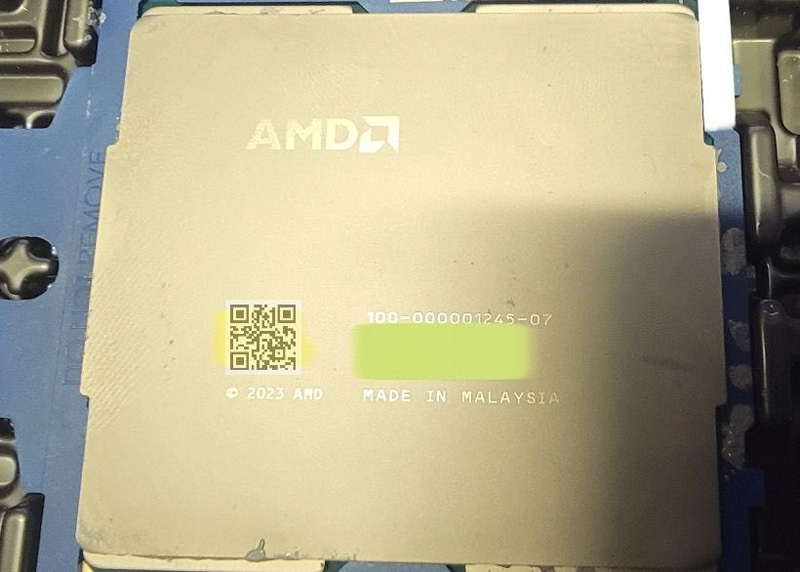

Источник изображений: YuuKi_AnS Теперь сообщается, что процессоры EPYC Turin будут использовать существующий сокет SP5 (LGA 6096). Они получат поддержку 12 каналов памяти DDR5-6000, а также стандартов CXL 2.0 и PCIe 5.0. Конструкция стандартных изделий EPYC Turin предусматривает использование 16 вычислительных чиплетов CCD (до восьми ядер в каждом) и унифицированного чиплета IOD, выполняющего роль хаба ввода-вывода. Количество ядер Zen 5 может достигать 128 (256 потоков инструкций). В изделиях с высокой плотностью задействованы 12 чиплетов CCD (до 16 ядер в каждом), а суммарное число ядер Zen 5с составляет до 192 (384 потока). Для каждого из вычислительных чиплетов предусмотрено наличие 32 Мбайт кеша L3, что в сумме даёт до 512/384 Мбайт. Показатель TDP достигает 550 Вт. На фотографиях якобы запечатлён инженерный образец чипа EPYC Turin с шифром 100-00001245-07. Процессор произведён в Малайзии в 2023 году.

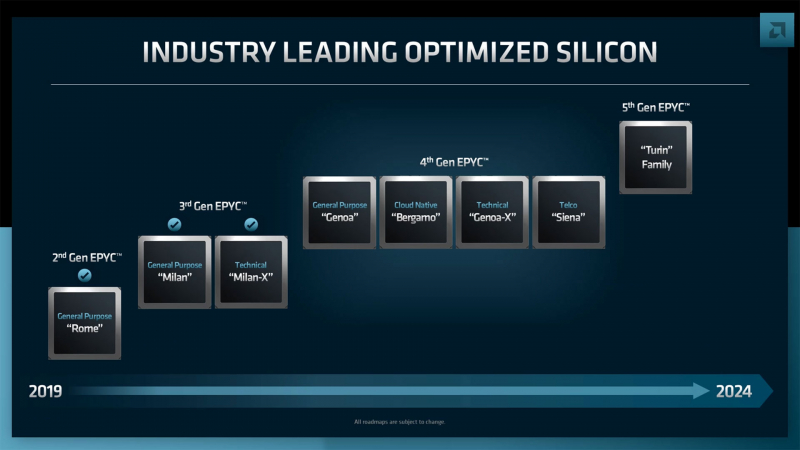

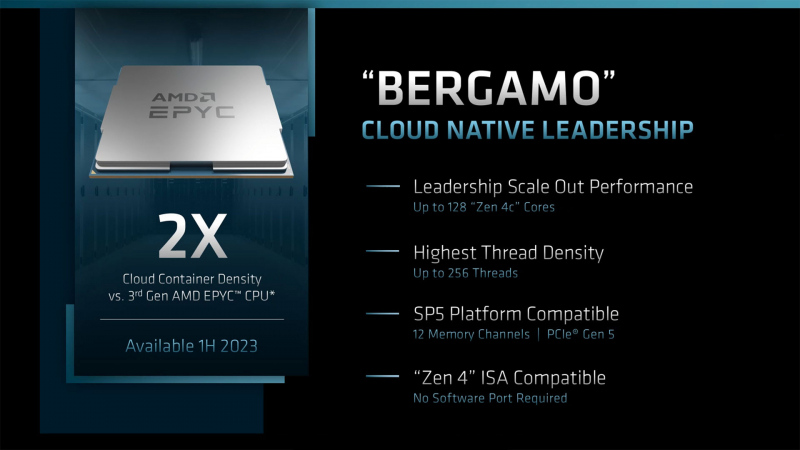

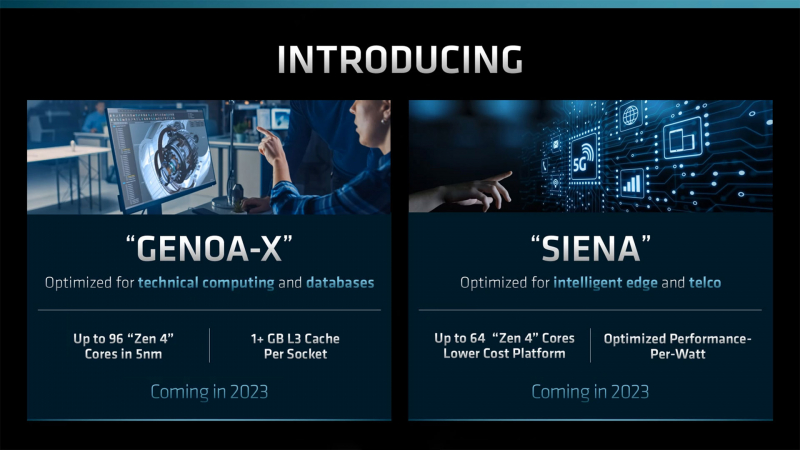

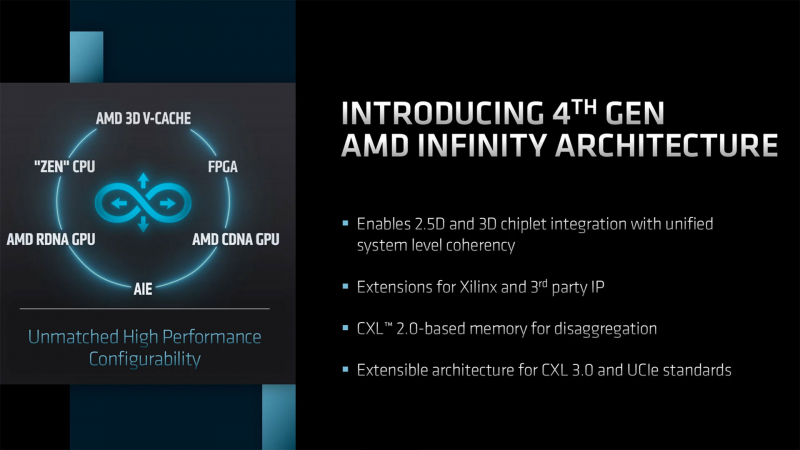

10.06.2022 [03:30], Игорь Осколков

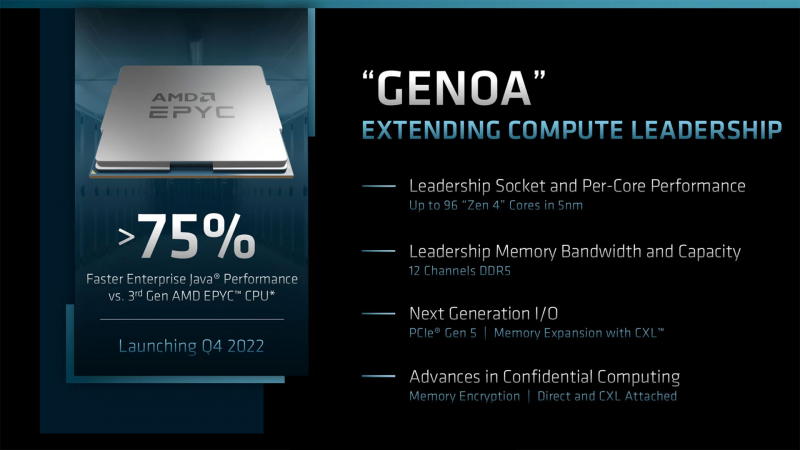

AMD анонсировала серверные процессоры EPYC Genoa-X, Siena и TurinНа прошедшем этим вечером отчётном мероприятии Financial Analysts Day 2022 компания AMD поделилась планами по дальнейшему развитию серверных процессоров EPYC. Речь шла как об уже анонсированных продуктах, так и о совершенно новых, предназначенных для неосвоенных ранее компанией сегментов. Наиболее значимым, хотя и наименее детальным, стал официальный анонс пятого поколения AMD EPYC под кодовым именем Turin (EPYC 7005), которое должно появиться до конца 2024 года. Они будут основаны на существенно переработанной архитектуре Zen 5 и изготавливаться по смешанному 3- и 4-нм техпроцессу. Обещано три разновидности кристаллов: обычные, с 3D V-Cache и «облачные» (Zen 5c), оптимизированные для повышения плотности размещения. Важно тут то, что таким образом сохранится преемственность между поколениями, что определённо порадует заказчиков. Но в ближайшее время нас ждёт выход AMD EPYC Genoa, который должен состояться в IV квартале текущего года. Эти 5-нм процессоры получат до 96 ядер Zen 4, 12 каналов DDR5, поддержку PCIe 5.0 и CXL. Причём сейчас уже явно говорится о возможности расширения системной памяти с помощью CXL. Переход на новый техпроцесс и увеличившееся в 1,5 раза количество ядер дали прирост производительности до +75% (в пример приводится тест Java SPECjbb). Для Genoa потребуется новый сокет SP5 (LGA6096). Он же будет готов принять ещё два варианта процессоров. Первый — это новенький Genoa-X, по названию которого легко догадаться, что это тот же Genoa (тоже до 96 ядер), снабжённый расширенным L3-кешем 3D V-Cache (от 1 Гбайт и более). Как и Milan-X, он будет ориентирован на специфический класс нагрузок, которые выигрывают от увеличения доступного объёма кеша. Это, например, расчётные задачи и СУБД. Genoa-X появятся в 2023 году. Тогда же стоит ждать и особую серию Bergamo. Эти процессоры, как и было обещано ранее, получат до 128 ядер (и 256 потоков), сохранив совместимость с сокетом SP5. Основаны они будут на 5-нм ядрах Zen 4c, который чем-то напоминают E-ядра в исполнении Intel. Однако набор команд у Zen 4c будет одинаков с Zen 4. Деталей устройства c-ядер AMD снова не раскрыла, но можно предположить, что у них переработана иерархия кешей. Предназначены они для гиперскейлеров, которым важна плотность размещения ресурсов, а не только производительность В 2023 году появятся и «малые» EPYC’и под кодовым названием Siena. Они оптимизированы с точки зрения энергоэффективности и предлагают до 64 ядер Zen 4. Siena ориентированы на периферийные вычисления и телеком-сегмент. Подробностей о них пока тоже мало. Не исключено, что мы увидим и гибриды наподобие Ice Lake-D, включающие интегрированные «умные» сетевые контроллеры. Существенным для всех новинок станет использование архитектуры Zen 4 (4 и 5 нм), которая, помимо ожидаемого прироста производительности, получит новые возможности. Среди них — поддержка AVX-512 (возможно, не самого полного набора) и новых инструкций для ИИ-нагрузок, которыми Intel хвасталась в течение нескольких лет. Но что ещё более важно, Zen 4 получат четвёртое поколение интерконнекта Infinity Architecture, который позволит более плотно связать различные чиплеты, причём и на уровне «кремния» (2.5D- и 3D-упаковка). А это открывает путь к эффективной компоновке различных функциональных модулей с поддержкой когерентности на уровне всего чипа — AMD подтвердила возможность интеграции FPGA Xilinx и IP-блоков сторонних компаний. Новый интерконнект также совместим с CXL 2.0, что важно для работы с памятью, а будущие версии получат поддержку CXL 3.0 и UCIE. Именно четвёртое поколение Infinity позволило AMD создать свои первые серверные APU Instinct MI300. |

|