Материалы по тегу: synopsys

|

11.03.2024 [16:47], Алексей Степин

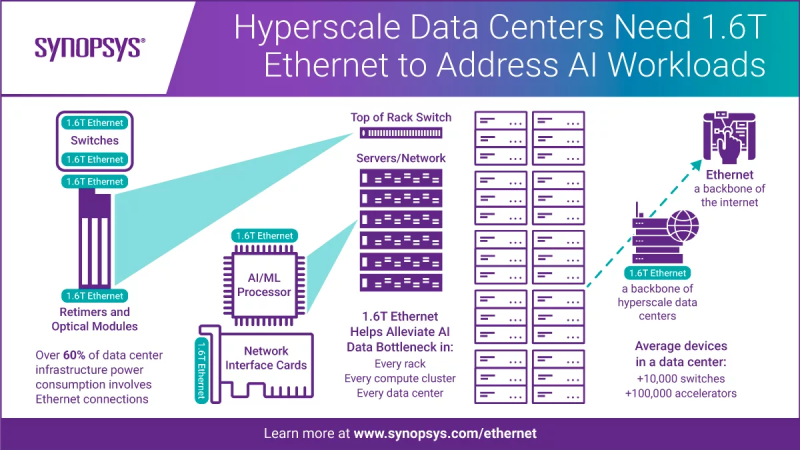

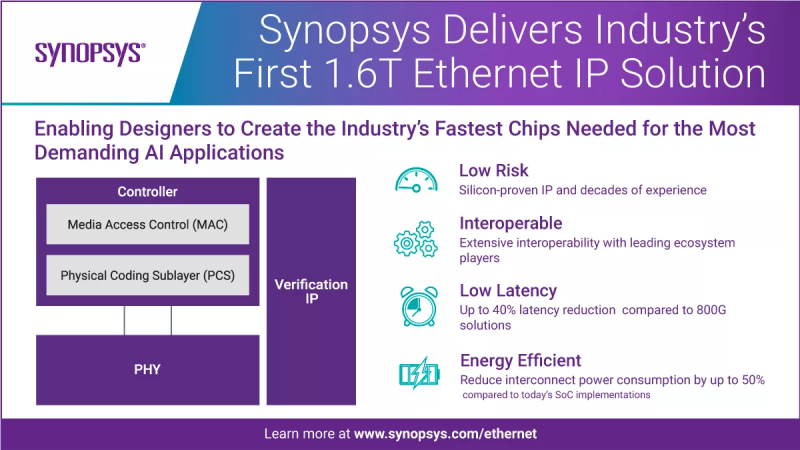

Synopsys завершила разработку платформы Ethernet 1,6 Тбит/сИзвестный разработчик микроэлектроники, компания Synopsys сообщила о завершении работ над новым сверхскоростным вариантом Ethernet, способным работать на скорости 1,6 Тбит/с, что вдвое превышает достигнутые коммерческими решениями на сегодня скорости. Эта разработка нацелена главным образом на рынок крупных ЦОД, особенно связанных с ИИ-технологиями, предъявляющими высокие требования к характеристикам сетевых каналов и интерконнектов. В настоящее время стандарт 1.6TbE не ратифицирован IEEE, и случится это не ранее 2026 года, но Synopsys считает, что применение её наработок в этой области позволит производителям микрочипов начать работу над созданием соответствующих контроллеров уже сейчас. Предварительная версия стандарта 802.3dj, описывающего базовые характеристики таких устройств, должна быть завершена уже в этом году. Дизайн IP-блоков, созданный Synopsys, базируется именно на 802.3dj. Он предусматривает скорости 4 × 400 Гбит/с, 2 × 800 Гбит/с, либо один канал со скоростью 1,6 Тбит/с. В разработке используются блоки SerDes со скоростью 112 и 224 Гбит/с, отвечающие спецификациям OIF-112G и OIF-224G соответственно. В IP-решении Synopsys используются трансмиттеры PAM4, в которых реализована продвинутая обработка сигнала (feed-forward equalization), ресиверы же содержат продвинутый DSP. Это сочетание позволяет соединению работать при потере сигнала в канале, составляющей 45 дБ. Synopsys утверждает, что её технологии позволят реализовать Ethernet со скоростью 1,6 Тбит/с с 50 % экономией площади кремния. Продвинутая архитектура коррекции ошибок при этом должна обеспечить латентность на 40 % ниже в сравнении с классической реализацией. В состав решения Synopsys входят блоки MAC, PCS, контроллер физического уровня (PHY) на основе прошедших тестирование и доказавших свою эффективность SerDes-блоков 224G, а также IP-модуль верификации, который должен помочь разработчикам чипов ускорить и упростить разработку новых сверхскоростных Ethernet-чипов. Все IP-компоненты доступны сейчас и ими уже воспользовались многочисленные клиенты, сообщает Synopsys. Новая разработка Synopsys получила одобрение со стороны консорциума Ethernet.

30.11.2023 [14:15], Сергей Карасёв

Выручка Synopsys бьёт рекорды, а чистая прибыль быстро растётКомпания Synopsys обнародовала показатели работы в IV квартале и 2023 финансовом году в целом, который был завершён 31 октября. Американский разработчик САПР для электроники зафиксировал рекордную выручку и показал значительный рост чистой прибыли. За трёхмесячный период Synopsys получила $1,6 млрд выручки, что является историческим максимумом. Это на 25 % больше результата за последнюю четверть 2022 финансового года, когда показатель равнялся приблизительно $1,3 млрд. Компания подчёркивает, что благодаря активным исследованиям и разработкам смогла улучшить показатели деятельности даже в условиях кризиса и макроэкономических неопределённостей. Чистая квартальная прибыль в годовом исчислении поднялась более чем в два раза — со $153,5 млн до $349,2 млн. Прибыль в пересчёте на одну ценную бумагу составила $2,26 против $0,99 годом ранее. Выручка по итогам 2023 финансового года в целом также оказалась рекордной — примерно $5,8 млрд. Для сравнения: годом ранее Synopsys получила около $5,1 млрд. Таким образом, рост оказался на уровне 15 %. Чистая годовая прибыль достигла $1,2 млрд, или $7,92 на акцию, по сравнению с $984,6 млн, или $6,29 на одну ценную бумагу, в 2022 финансовом году. В I четверти 2024 финансового года, которая продлится до 31 января, Synopsys рассчитывает получить выручку от $1,63 млрд до $1,66 млрд и показать при этом прибыль в диапазоне от $2,4 до $2,5 на акцию. В наступившем финансовом году в целом выручка, как ожидается, составит от $6,57 млрд до $6,63 млрд, чистая прибыль — от $9,07 до $9,25 на одну ценную бумагу.

13.11.2023 [13:56], Сергей Карасёв

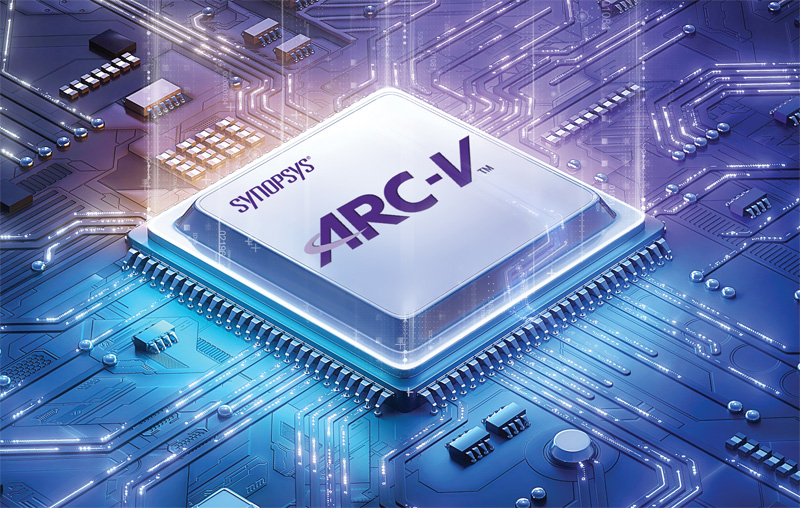

Synopsys представила ядра ARC-V на архитектуре RISC-VКомпания Synopsys анонсировала процессорные ядра ARC-V на архитектуре RISC-V, которые будут доступны для лицензирования сторонним разработчикам. Заказчики смогут воспользоваться сопутствующими инструментами, включая средства автоматизации проектирования электронных устройств на базе ИИ Synopsys.ai. В семейство Synopsys ARC-V Processor IP вошли модификации с высоким и средним уровнями производительности, а также версия со сверхнизким энергопотреблением. Разработчики смогут воспользоваться платформой Synopsys MetaWare для создания эффективного и высокооптимизированного кода.

Источник изображения: Synopsys Кроме того, анонсировано ядро Synopsys ARC-V Functional Safety (FS) со встроенными аппаратными функциями безопасности для обнаружения системных ошибок. Говорится об уровнях безопасности ASIL B и ASIL D. Изделие разработано на основе системы управления качеством (QMS) Synopsys, сертифицированной по стандарту ISO 9001. А пакет MetaWare Development Toolkit for Safety поможет разработчикам ускорить написание кода, соответствующего стандарту ISO 26262. 32-битное ядро Synopsys ARC-V RMX для встраиваемых систем станет доступно во II квартале 2024 года. 32-битное ядро реального времени Synopsys ARC-V RHX и 64-битное ядро Synopsys ARC-V RPX IP планируется выпустить во второй половине следующего года. Synopsys также сообщила, что её представитель войдёт в состав совета директоров и технический руководящий комитет некоммерческой организации RISC-V International, которая занимается координацией разработки данной архитектуры.

06.10.2023 [14:45], Сергей Карасёв

Российский разработчик НПЦ «Элвис» судится с Synopsys из-за отказа от техподдержкиНаучно-производственный центр «Электронные вычислительно-информационные системы» (НПЦ «ЭЛВИС»), российский разработчик микросхем, по сообщению TAdviser, судится с российским представительством Synopsys. Американский разработчик САПР для электроники обвиняется в отказе от предоставления предоплаченных услуг техподдержки. Согласно материалам дела, в декабре 2021 года НПЦ «Элвис» и Synopsys заключили соглашение о лицензировании и сопровождении ПО на сумму около 419,3 млн руб. При этом стоимость техподдержки составила приблизительно 108,5 млн руб. Однако с марта 2022-го в условиях сложившейся геополитической обстановки Synopsys прекратила обслуживание НПЦ «Элвис»: российский разработчик даже не мог зайти в личный кабинет на сайте solvnet.synopsys.com. В мае 2022-го Synopsys уведомила НПЦ «Элвис» по электронной почте, о том, что планирует прекращение свой деятельности в течение 2–3 месяцев. На требование НПЦ «Элвис» обосновать причину неоказания услуг компания Synopsys не ответила, после чего российская сторона потребовала выплатить сумму неосновательного обогащения с 1 апреля по декабрь 2022 включительно, а также проценты за пользование чужими денежными средствами.

Источник изображения: НПЦ «ЭЛВИС» Однако суд посчитал, что размер стоимости, подлежащей возврату, должен быть пропорционален периоду до прекращения обязательственных отношений, то есть, с 10 июля 2022 года (уведомление об отказе от договора в июне плюс 30 дней). Таким образом, компенсация составила 51,2 млн руб., что меньше суммы, затребованной НПЦ «Элвис». В сентябре 2023 года кассационный суд, как и две предыдущих инстанции, отказался удовлетворить требования российской компании в полном объёме.

22.03.2023 [00:22], Сергей Карасёв

Решения NVIDIA в области вычислительной литографии заложат основу для выпуска чипов нового поколенияNVIDIA в рамках GTC 2023 объявила о новом решении, которое привносит возможности ускорения работы в сферу вычислительной литографии. Это позволит крупным игрокам полупроводниковой отрасли, таким как ASML, TSMC и Synopsys, ускорить разработку и производство микросхем нового поколения по мере приближения характеристик чипов к физическим ограничениям. Речь идёт о библиотеке NVIDIA cuLitho для вычислительной литографии. Говорится, что её интеграцией уже занимаются контрактный производитель TSMC, а также фирма Synopsys, работающая в области САПР для проектирования электроники. Производитель оборудования ASML также сотрудничает с NVIDIA в области GPU и cuLitho. Эти компании намерены встроить cuLitho в своё ПО, производственные процессы и системы на базе чипов с архитектурой NVIDIA Hopper. Говорится, что предприятия, использующие cuLitho, смогут ежедневно производить в 3–5 раз больше фотошаблонов при в 9 раз меньших затратах энергии по сравнению с традиционными методами.

Источник изображения: NVIDIA Предполагается, что решение NVIDIA позволит проектировать микросхемы по более «тонкому» техпроцессу, нежели это возможно сейчас. Кроме того, сократится время выхода продуктов на рынок и повысится энергоэффективность крупных дата-центров, отвечающих за управление производственными процессами. В частности, с применением cuLitho может быть заложена основа для выпуска изделий с нормами 2 нм и менее. Утверждается, что, работая на базе GPU разработки NVIDIA, платформа cuLitho обеспечивает скачок производительности до 40 раз по сравнению с обычной литографией. Это даёт возможность 500 системам NVIDIA DGX H100 заменить 40 000 CPU благодаря параллельной обработке различных элементов вычислительной литографии. Кроме того, значительно снижается энергопотребление ЦОД и сокращается негативное воздействие на окружающую среду.

08.06.2022 [18:20], Алексей Степин

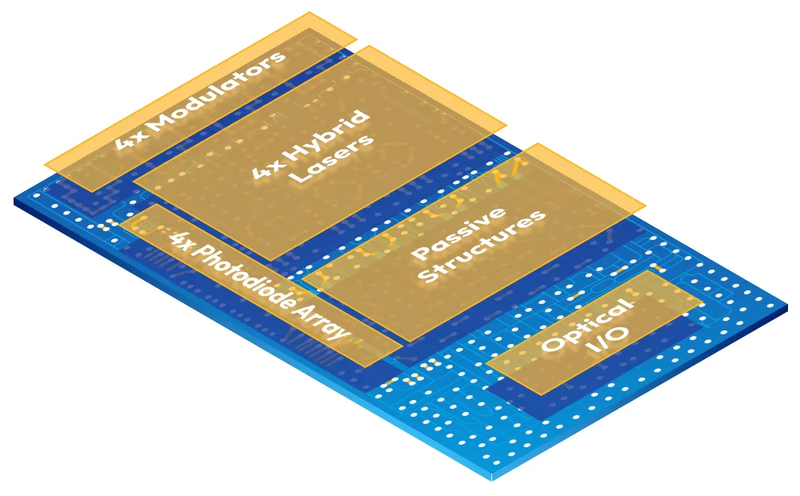

Synopsys и Juniper Networks объединились для освоения кремниевой фотоникиЗа фотоникой будущее сетей и интерконнектов, это становится всё очевиднее по мере того, как игроки на рынке микроэлектроники создают альянсы для освоения этой «территории». Уже известен союз Ayar Labs и NVIDIA, теперь очередь дошла до Synopsys и крупного производителя сетевого оборудования Juniper Networks. Эти компании объявили о заключении стратегического союза в области освоения фотонных технологий. Детищем альянса стала новая компания, названная OpenLight, в её состав вошло одно из подразделений Juniper, однако 75% активов OpenLight принадлежит Synopsys.

Источник: OpenLight Название хорошо отражает цели OpenLight — речь идёт о разработке архитектурно открытых решений кремниевой фотоники, которые могут создаваться силами сторонних компаний на мощностях Tower Semiconductor. В планах компании создание высокопроизводительных фотонных чипов для рынка телекоммуникаций, систем лазерной навигации, здравоохранения, высокопроизводительных вычислений и оптических процессоров. Сердцем этих разработок станет электронно-оптический модулятор на основе фосфида индия (InP), обеспечивающий меньшие потери сигнала и лучшие характеристики в сравнении с традиционными кремниевыми аналогами. Ключевой особенностью также считается использование интегрированного лазера, чего нет, например, у Ayar Labs. Технологический процесс PH18DA, используемый Tower Semiconductor позволит добиться такой интеграции, что в перспективе сделает кремниевую фотонику дешевле и доступнее.

Технологии OpenLight позволят создавать монолитные электронно-оптические чипы. Источник: OpenLight Рабочие образцы первых оптических трансиверов класса 400G/800G на базе новой технологии, по словам представителей OpenLight, можно будет ожидать уже летом этого года. Тогда же компания обещает выпустить и первый многокомпонентный «кремний» на базе техпроцесса PH18DA — на одной пластине будут находиться чипов разных разработчиков. Такой подход позволит оптимизировать производственные расходы и снизить себестоимость готовых изделий. Стоит отметить, что Tower Semiconductor вскоре будет приобретена Intel, которая (как и NVIDIA) кровно заинтересована в разработке кремниево-фотонных технологий и уже успела инвестировать в Ayar Labs вместе с GlobalFoundries, HPE, NVIDIA и Lockheed Martin. В прошлом году Cisco, ещё один крупный производитель сетевого оборудования, поглотил Acacia, компанию-разработчика в области кремниевой фотоники. |

|