Материалы по тегу: risc-v

|

13.11.2023 [13:56], Сергей Карасёв

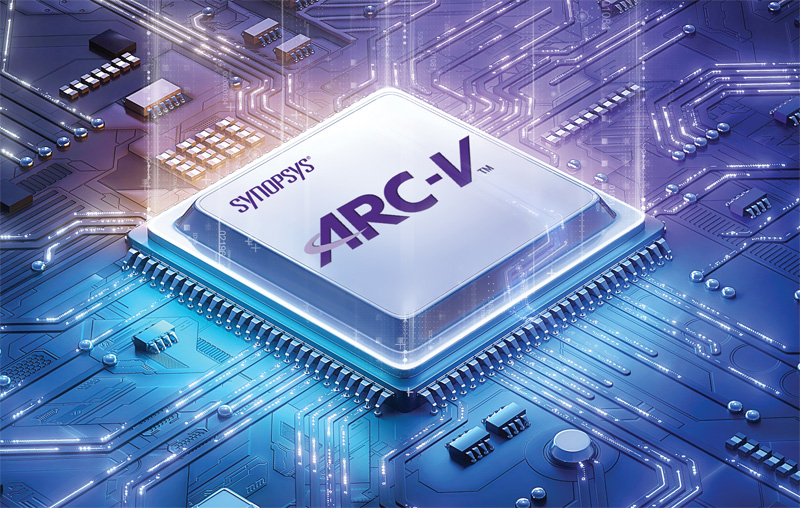

Synopsys представила ядра ARC-V на архитектуре RISC-VКомпания Synopsys анонсировала процессорные ядра ARC-V на архитектуре RISC-V, которые будут доступны для лицензирования сторонним разработчикам. Заказчики смогут воспользоваться сопутствующими инструментами, включая средства автоматизации проектирования электронных устройств на базе ИИ Synopsys.ai. В семейство Synopsys ARC-V Processor IP вошли модификации с высоким и средним уровнями производительности, а также версия со сверхнизким энергопотреблением. Разработчики смогут воспользоваться платформой Synopsys MetaWare для создания эффективного и высокооптимизированного кода.

Источник изображения: Synopsys Кроме того, анонсировано ядро Synopsys ARC-V Functional Safety (FS) со встроенными аппаратными функциями безопасности для обнаружения системных ошибок. Говорится об уровнях безопасности ASIL B и ASIL D. Изделие разработано на основе системы управления качеством (QMS) Synopsys, сертифицированной по стандарту ISO 9001. А пакет MetaWare Development Toolkit for Safety поможет разработчикам ускорить написание кода, соответствующего стандарту ISO 26262. 32-битное ядро Synopsys ARC-V RMX для встраиваемых систем станет доступно во II квартале 2024 года. 32-битное ядро реального времени Synopsys ARC-V RHX и 64-битное ядро Synopsys ARC-V RPX IP планируется выпустить во второй половине следующего года. Synopsys также сообщила, что её представитель войдёт в состав совета директоров и технический руководящий комитет некоммерческой организации RISC-V International, которая занимается координацией разработки данной архитектуры.

09.11.2023 [14:56], Сергей Карасёв

Китай развернул первый облачный кластер на базе RISC-VШаньдунский университет в Китае, по сообщению HPC Wire, развернул в облаке первый коммерческий кластер с серверами, оснащёнными процессорами на открытой архитектуре RISC-V. Это очередная попытка КНР сократить зависимость от зарубежных технологий в свете возрастающего санкционного давления со стороны США. В составе запущенной платформы задействованы процессоры Sophgo SOPHON SG2042 с 64 ядрами RISC-V и 64 Мбайт кеша L3. Тактовая частота достигает 2,0 ГГц. Реализована поддержка интерфейса PCIe Gen 4. В составе системы в общей сложности объединены 48 узлов, что в сумме даёт 3072 ядра. Система, как отмечается, предназначена прежде всего для учебных и исследовательских целей. Однако она также поддерживает работу определённых облачных инстансов.

Источник: RISC-V Summit У Китая есть комплексный план по разработке собственных чипов RISC-V. В этом году Министерство науки и технологий КНР профинансировало разработку таких чипов, и многие университеты и научные лаборатории также подключились к созданию таких изделий. В мае Китайская академия наук представила 2-ГГц процессор Xiangshan на архитектуре RISC-V, тогда как ведущие китайские RISC-V-разработчики сформировали патентный альянс. Говорится, что ведётся разработка изделия Xiangshan-v3: в проекте принимают участие крупные китайские компании, включая Alibaba, Tencent и ZTE. По производительности новый чип будет сопоставим с Arm Neoverse-N2. Ранее говорилось, что американские санкции против Китая могут ускорить распространение архитектуры RISC-V. Вместе с тем высказываются опасения, что запуск Пекином облачного RISC-V-кластера может привлечь дополнительное внимание со стороны регуляторов США. Законодатели в Палате представителей призвали запретить американским компаниям работать с китайскими организациями над технологиями RISC-V.

09.11.2023 [03:15], Алексей Степин

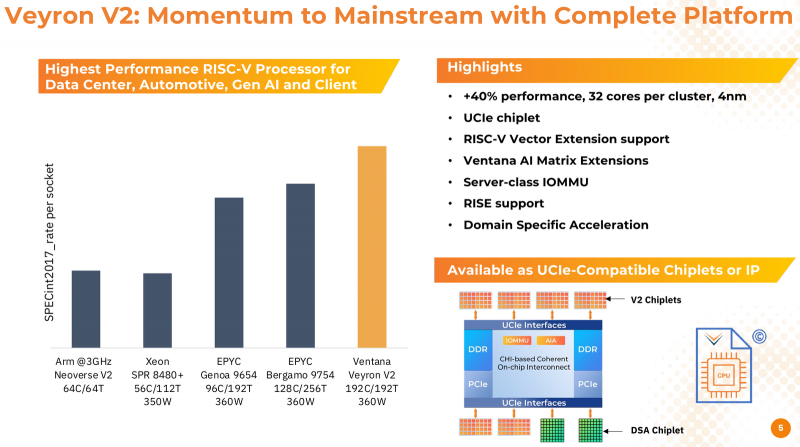

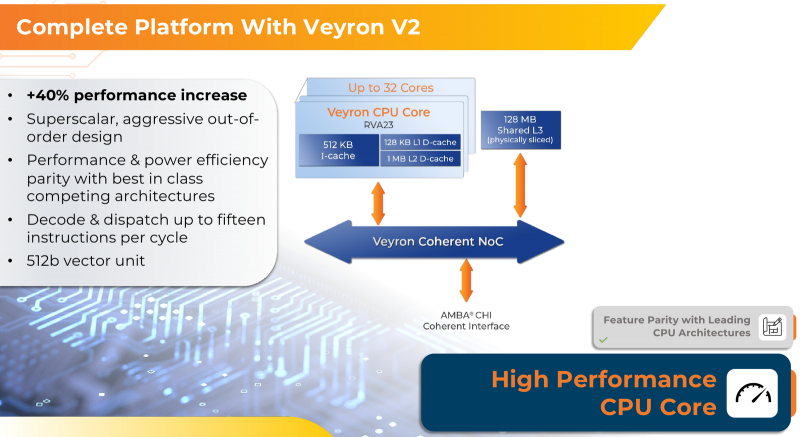

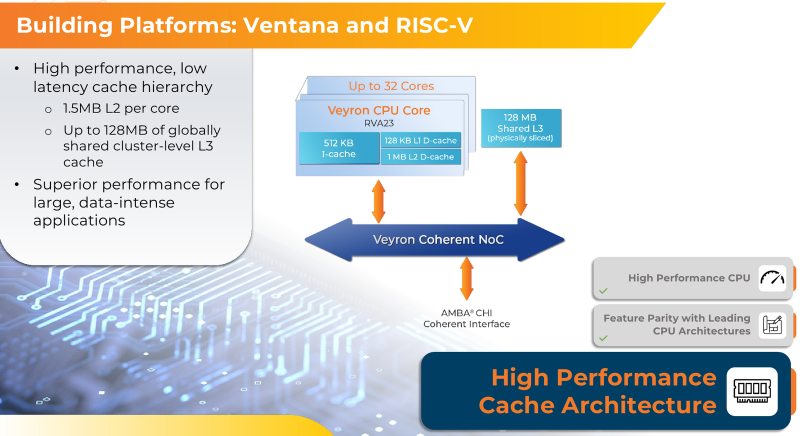

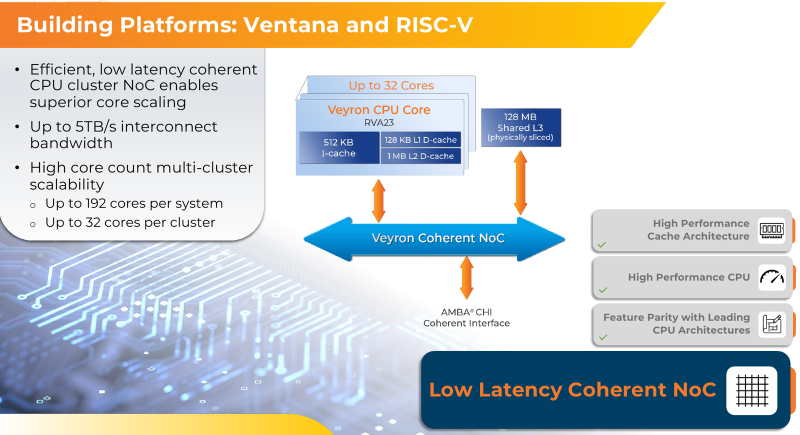

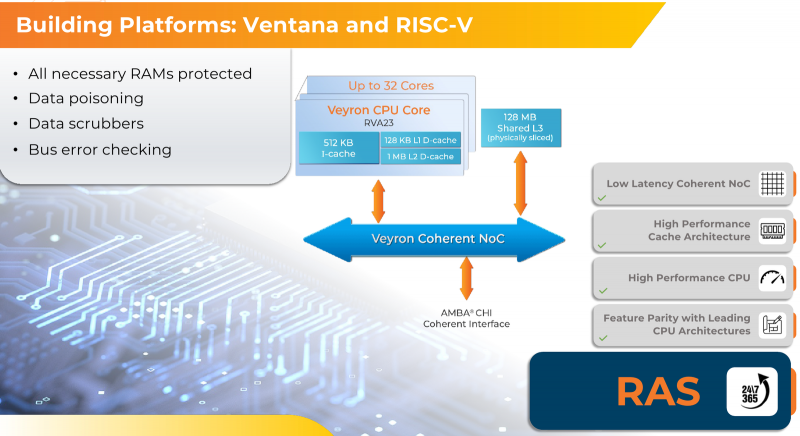

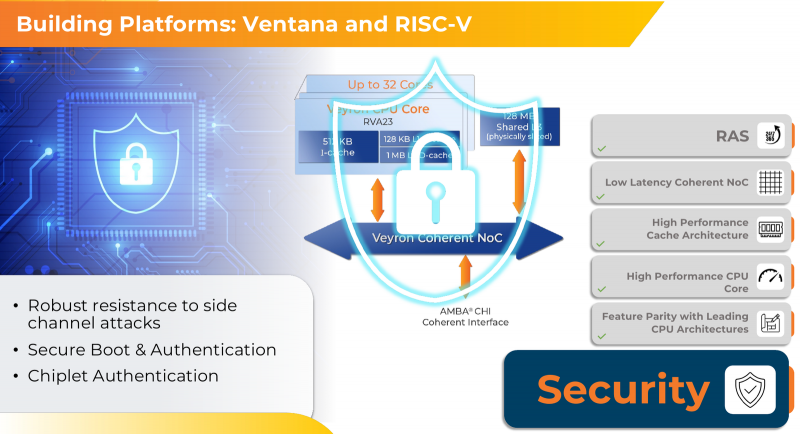

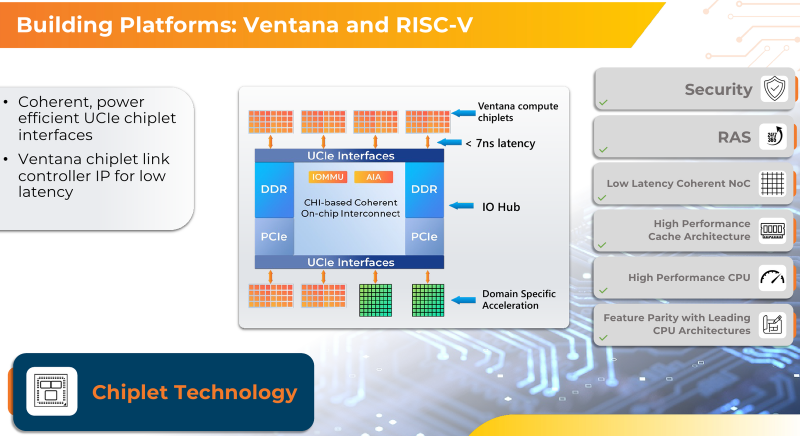

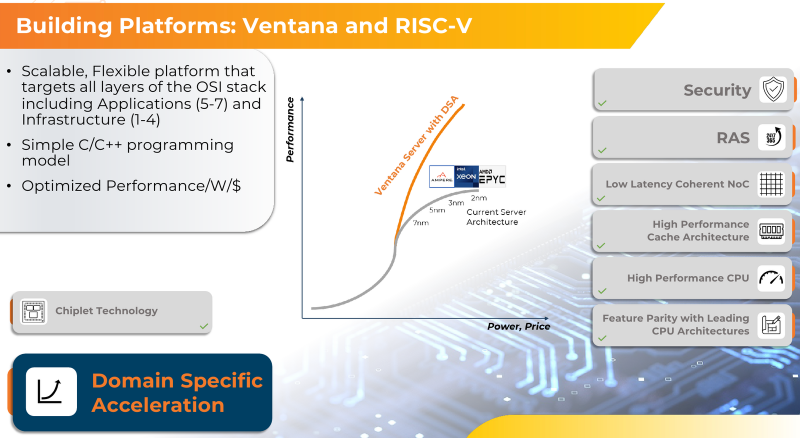

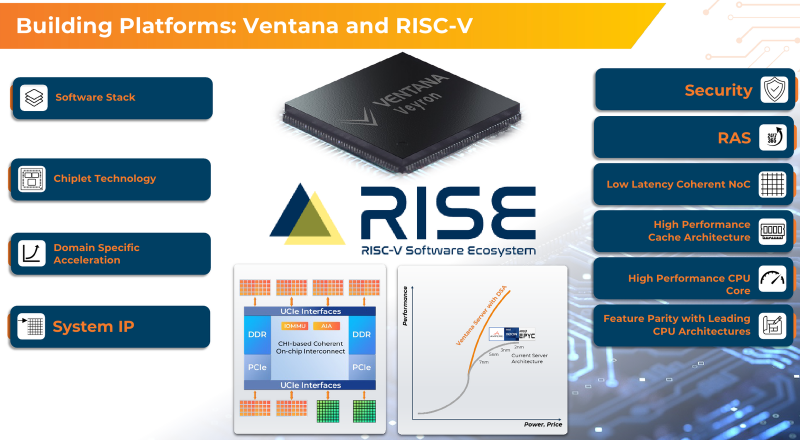

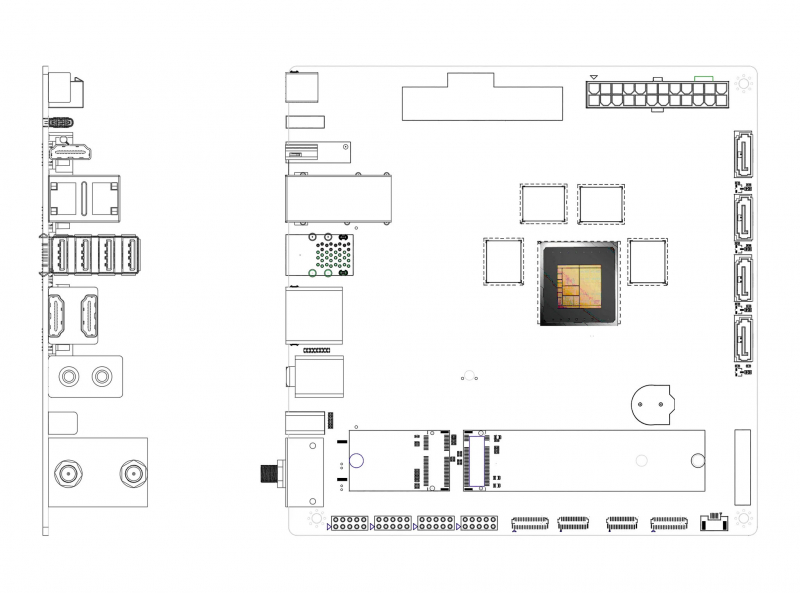

RISC-V с приправой: модульные 192-ядерные серверные процессоры Ventana Veyron V2 можно дополнить ускорителямиВ 2022 года компания Ventana Micro Systems анонсировала первые по-настоящему серверные RISC-V процессоры Veyron V1. Анонс чипов, обещающих потягаться на равных с лучшими x86-процессорами с архитектурой x86, прозвучал громко. Популярности, впрочем, Veyron V1 не снискал, но на днях компания анонсировала второе поколение чипов Veyron V2, более полно воплотившее в себе принципы модульного дизайна и получившее ряд усовершенствований. Как и в первом поколении, компания-разработчик продолжает придерживаться концепции «процессора-конструктора» с чиплетным дизайном. В центре 4-нм Veyron V2 по-прежнему лежит I/O-хаб на базе AMBA CHI, охватывающий контроллеры памяти и шины PCI Express, а также блоки IOMMU и AIA. К нему посредством интерфейса UCIe подключаются вычислительные чиплеты. Латентность UCIe-подключения составляет менее 7 нс.

Источник изображений здесь и далее: Ventana Micro Systems Чиплеты эти могут быть разных видов: либо с ядрами общего назначения (по 32 ядра на чиплет), образующие собственно процессор Veyron V2, либо содержащие специфические сопроцессоры под конкретную задачу (domain-specific acceleration, DSA). Последние могуть быть представлены FPGA, ИИ-ускорителями и т.д. Более того, Ventana по желанию заказчика может оптимизировать и I/O-хаб для повышения эффективности работы ядер CPU с сопроцессорами. В классическом варианте Veyron V2 может иметь до шести чиплетов с RV64GC-ядрами V2, что в сумме даёт 192 ядра. Поддержка SMT отсутствует. Удельная производительность в пересчёте на ядро получается несколько ниже, чем у AMD Zen 4c, но согласно результатам тестов, предоставленных Ventana, 192-ядерный Veyron V2 заметно опережает AMD EPYC Bergamo 9754 (128C/256T) при аналогичном теплопакете в 360 Вт. Столь неплохой результат достигнут за счёт оптимизации архитектуры Veyron: по сравнению с первым поколением говорится о 40 % прибавке производительности. Что немаловажно, во втором поколении процессоров Veyron была реализована поддержка 512-бит векторных расширений, фирменных матричных расширений, а также целого ряда других спецификаций. В целом ради совместимости разработчики предпочли остаться в рамках общего профиля RVA23. Сами ядра V2 используют суперскалярный дизайн с агрессивным внеочередным исполнением и продвинутым предсказанием ветвлений. Возможно декодирование и обработка до 15 инструкций за такт. Объём L1-кешей составляет 512 Кбайт для инструкций и 128 Кбайт для данных, дополнительно каждое ядро имеет свой кеш L2 объёмом 1 Мбайт. Общий для всего 32-ядерного чиплета L3-кеш имеет объём 128 Мбайт. Производительность внутренней когерентной шины составляет до 5 Тбайт/с. Позиционируемый в качестве решения для гиперскейлеров, крупных ЦОД и HPC, Veyron V2 имеет развитые средства предотвращения ошибок и защиты данных, от ECC-кешей и поддержки Secure Boot до аутентификации на уровне чиплета и продвинутых RAS-функций. Кроме того, реализована защита от атак по сторонним каналам. Несмотря на то, что мир RISC-V пока ещё похож на «Дикий Запад», Ventana старается опираться на развитые и популярные стандарты: в частности, это выражается в применении UCIe для подключения чиплетов, поддержку гипервизоров первого и второго типа, вложенную виртуализацию и совместимость с программной экосистемой RISC-V RISE. Подход Ventana позволит избежать недостатков, свойственных дискретным PCIe-ускорителям (высокая латентность, энергопотребление и стоимость) и сложным монолитным SoC (очень высокая стоимость разработки и сроки), снизить время и стоимость стоимость новых решений, а также обеспечить более низкий уровень энергопотребления. В общем, компания явно целится в гиперскейлеров. Видение сценариев применения DSA у Ventana очень широкий — от БД-ускорителей и блоков компрессии-декомпрессии данных до поддержки специфических алгоритмов в задачах аналитики и транскодеров в системах доставки контента. Также становятся ненужными дискретные DPU. Первым партнёром Ventana стала Imagination Technologies, крупный разработчик GPU. В качестве вариантов физической реализации новой платформы Ventana предлагает компактный 1U-сервер, содержащий один чип Veyron V2 со 192 ядрами, работающими на частотах до 3,6 ГГц, и 12 каналами DDR5-5600. Вероятнее всего, производителем новой платформы станет GIGABYTE. Ожидать первых поставок следует не ранее II квартала 2024 года. В целом, видение высокопроизводительной модульной платформы, продвигаемое Ventana, выглядит перспективно, а упор на применение DSA может выгодно отличать её большинства Arm-серверов, конкурирующих с решениями Intel/AMD лоб в лоб. Вопрос лишь в поддержке со стороны разработчиков программного обеспечения — и здесь может сыграть ставка разработчиков на максимально открытые, широкие стандарты.

07.11.2023 [01:43], Руслан Авдеев

Китайская T-Head представила Zhenyue 510 — PCIe 5.0 контроллер на базе RISC-V для серверных SSDКомпания T-Head, подразделение китайского техногиганта Alibaba Group Holding, представила SSD-контроллер PCIe 5.0 с ядрами на базе открытой архитектуре RISC-V. По данным Alibaba Cloud, контроллер Zhenyue 510 будет использоваться в накопителях корпоративного уровня и найдёт применение в облачных ЦОД самой Alibaba для обслуживания проектов, связанных обучением ИИ, работой СУБД, анализом больших данных, виртуализацией и т.п. Новый контроллер, по словам создателей, обеспечивает на 30 % более низкую задержку в сравнении с аналогичными решениями. Чип поддерживает 16 каналов NAND, обеспечивает скорость до 14 Гбайт/с и 3,4 млн IOPS (если это не опечатка), предлагает эффективные LDPC-алгоритмы и поддержку SR-IOV. Новинка T-Head не одинока — в сентябре InnoGrit начала массовый выпуск YR S900, первого китайского контроллера PCIe 5.0 для серверных SSD, тоже сделанного на базе RISC-V. В 2019 году T-Head уже дебютировала с IoT-чипом XuanTie 910 на базе RISC-V, причём по решению Alibaba это IP-блоки стали открытыми. Также T-Head разработали ИИ-ускоритель Hanguang 800 (2019 год) и 128-ядерный серверный Arm-процессор Yitian 710 (2021 год), предназначенные для облачных сервисов. Решения используются преимущественно в пределах КНР. Считается, что благодаря открытости RISC-V Китай может получить новые возможности развития полупроводниковой отрасли и снизить зависимость от иностранных владельцев интеллектуальной собственности, а это особенно важно на фоне эскалации технологического соперничества между США и КНР. Американские законотворцы даже призывают принять меры по ограничению применения архитектуры RISC-V по соображениям национальной безопасности.

22.10.2023 [17:29], Алексей Степин

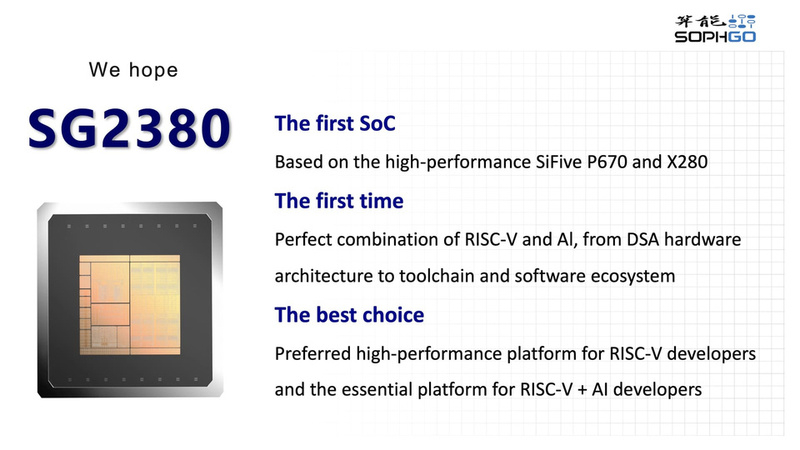

Sophgo представила 16-ядерный процессор SG2380 с архитектурой RISC-V и встроенным ИИ-ускорителемЭкосистема RISC-V наращивает темпы развития: от скромных SBC с одно- и двухъядерными чипами с производительностью уровня Raspberry Pi до вполне «взрослых» многоядерных решений. Одной из компаний, развивающих это направление, является Sophgo. Сейчас Sophgo совместно с Milk-V анонсировала новую плату, оснащённую 16-ядерным процессором SG2380 с интегрированным ИИ-сопроцессором. Ранее Sophgo уже дебютировала с любопытной платой Pioneer, оснащённой 64-ядерным процессором с архитектурой RISC-V и даже показала рабочую станцию разработчика Pioneer Box на её основе. Также компания демонстрировала двухсокетный сервер с 128 ядрами RISC-V. Новинка, Milk-V Oasis, выглядит скромнее, но также весьма небезынтересна. В ней используется 16-ядерный процессор SG2380 с ядрами SiFive Performance P670, работающими на частоте 2,5 ГГц. В дополнение к ним в составе ЦП работает восьмиядерный ИИ-ускоритель на базе SiFive Intelligence X280 с производительностью 20 Топс на вычислениях INT8.

Источник изображений здесь и далее: Sophgo Процессор также располагает собственным GPU Imagination AXT-16-512 с поддержкой Vulkan 1.3, OpenGL 3.0 и OpenGL ES 3.x. Его производительность невысока, всего 0,5 Тфлопс/2 Топс, но для задач, характерных для интегрированной графики, этого достаточно. Видеочасть поддерживает декодирование 10-битного видео в форматах H.265/HEVC, H.264, AV1 и VP9, но аппаратного кодера чип не имеет.  На базе данного процессора Milk-V анонсировала плату Oasis в форм-факторе mini-ITX. Решение обещает до 64 Гбайт памяти LPDDR5 на скорости 5500 МТ/с, поддержку съёмных модулей UFS, полноценный разъём M.2 (PCIe 3.0 x4) и четыре порта SATA. Вывод видео осуществляется с помощью двух портов HDMI (4K@60), порта eDP с поддержкой тачскринов, либо посредством разъёмов MIPI DSI. Сетевая часть представлена двумя портами 2,5GbE, имеются разъёмы M.2 для установки модулей Wi-Fi 6 и 4G/5G-модема. Имеется полноценный слот PCIe x16 (логически PCIe 3.0 x8), 8 разъёмов DIO, 2 разъёма CAN Bus, а также широкий набор портов USB — два версии 3.0, два версии 2.0, два фронтальных версии 2.0 и порт USB-C с возможностью проброса DP. Судя по всему, плата предназначена для периферийных ИИ-платформ, робототехники и иных аналогичного рода задач. Также она может заинтересовать энтузиастов и разработчиков ПО для RISC-V в качестве настольной системы, недорогой альтернативы Pioneer. Стоимость новинки стартует от $120, но доступна она будет ещё не скоро — источники называют III квартал 2024 года. Тем не менее, уже можно оформить предварительный заказ.

12.10.2023 [12:44], Сергей Карасёв

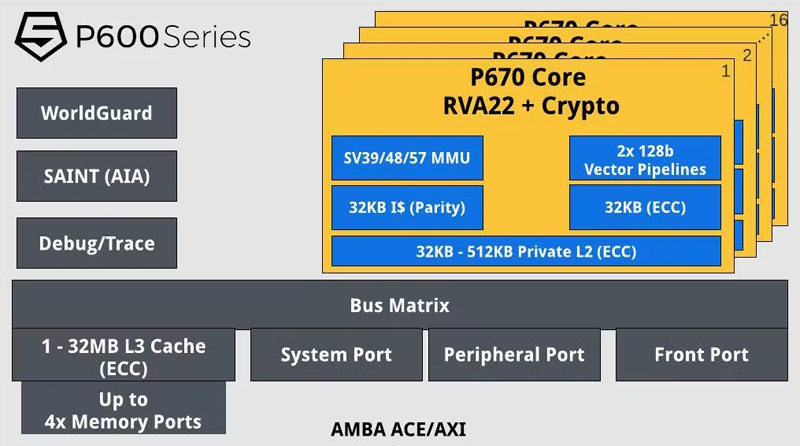

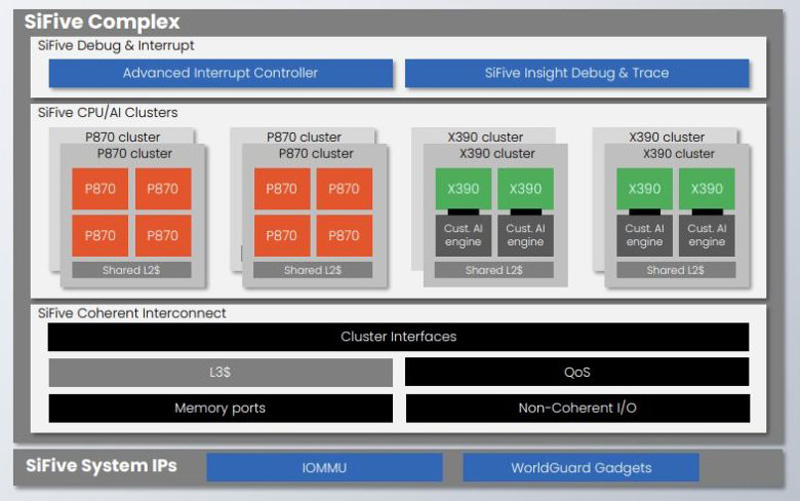

SiFive представила RISC-V ядро Performance P870 и NPU-блок Intelligence X390Компания SiFive анонсировала процессорное ядро Performance P870 с архитектурой RISC-V для высокопроизводительных клиентских приложений. Кроме того, дебютировал NPU-блок Intelligence X390 для задач машинного обучения и ИИ. Решение Performance P870, как утверждается, обеспечивает прирост производительности примерно на 50 % (specINT 2006) по сравнению с ядром предыдущего поколения. Тактовая частота не раскрывается, но, по имеющимся данным, она превышает 3 ГГц.

Источник изображения: SiFive В состав изделия входят два 128-бит векторных блока. На основе Performance P870 могут создаваться процессоры, насчитывающие до 32 ядер: это вдвое больше по сравнению с предшественником (Performance P670). Отмечается, что P870 может применяться для формирования гетерогонных SoC, также содержащих ядра P670 и P470. При этом каждый кластер использует общий кеш L2. Доступна и автомобильная версия Performance P870 с высокой степенью резервирования и отказоустойчивости. Новые ядра могут использоваться в сочетании с векторными процессорами в дата-центрах. В свою очередь, решение Intelligence X390, по заявлениям SiFive, обеспечивает 4-кратное увеличение быстродействия векторных вычислений по сравнению с NPU предыдущего поколения Intelligence X280. Поддерживаются 1024-битные векторные регистры (VLEN) с 512-битными путями данных (DLEN). SiFive не раскрыла поддерживаемые типы данных, но известно, что X280 поддерживает INT8, INT16, INT32, FP16, FP32 и FP64. Комбинированное решение, состоящее из P870 и X390, предоставляет разработчикам гибкую платформу для приложений генеративного ИИ.

12.10.2023 [02:00], Руслан Авдеев

США хотели бы ограничить доступ отдельным странам к архитектуре RISC-VОткрытая архитектура RISC-V, сегодня доступная любым разработчикам микрочипов, может исчезнуть из свободного доступа по инициативе США. Американские власти рассматривают возможность ограничить недружественным компаниям участие в международных сообществах RISC-V. Как сообщает «Коммерсантъ», это может создать проблемы российскому бизнесу, планирующему выпускать продукцию на соответствующей архитектуре. Ранее отечественные компании, например, отлучили от OpenRAN. Открытая архитектура RISC-V появилась в Калифорнийском университете в Беркли и сегодня может использоваться совершенно свободно и бесплатно, в том числе в коммерческих проектах. Хотя в современных продуктах ядра RISC-V чаще предназначены для задач, требующих невысокой производительности, считается, что архитектура имеет большой потенциал для борьбы с x86 или Arm. Для синхронизации работ представители компаний участвуют в альянсах, крупнейшим из которых является RISC-V International. Несколько лет назад альянс «переехал» из США в Швейцарию из-за опасений возможных ограничений со стороны Вашингтона. По данным СМИ, получившим доступ к подготовленной «Альянсом RISC-V» программой развития архитектуры RISC-V в России, к 2025 году отечественные разработчики чипов выпустят прототипы высокопроизводительных процессоров на данной архитектуре, а после 2026 года может начаться уже серийное производство таких чипов. В альянс входят «Байкал Электроникс», «Синтакор», «Аквариус» и ряд других крупных компаний. По данным отраслевых источников, производством подобных чипов могут заняться, например, Yadro и «Байкал Электроникс». Прямо сейчас ряд американских конгрессменов требует ввести в отношении архитектуры экспортные ограничения. Хотя в первую очередь политики озабочены использованием RISC-V в китайских проектах, под вопросом может оказаться участие в международных альянсах российских разработчиков. При этом именно такие объединения задают общие стандарты. Если технические комитеты подобных альянсов перестанут принимать представителей российских дизайн-центров, разработка будет осложнена и последним придётся, как минимум, соблюдать стандарты, принятые без их участия. Впрочем, эксперты допускают использование обходных путей для сохранения присутствия в подобных объединениях. Некоторые утверждают, что достаточно будет создать промежуточное юридическое лицо на нейтральной территории вроде Гонконга. При этом сама RISC-V International заявила, что попытки ограничений со стороны правительств затормозят появление новых, улучшенных чипов и отбросят назад глобальную технологическую отрасль.

29.09.2023 [13:15], Сергей Карасёв

InnoGrit начала массовый выпуск первого китайского контроллера PCIe 5.0 для серверных SSDКитайская компания Yingren Technology (InnoGrit), по сообщению ресурса Tom's Hardware, организовала массовое производство первого в стране контроллера PCIe 5.0, предназначенного для создания SSD корпоративного класса. Изделие получило обозначение YR S900. Новинка представляет собой четырехканальный контроллер SSD, основанный на архитектуре RISC-V. Выбор RISC-V объясняется в том числе напряжёнными отношениями между США и КНР: в данном случае на изделие не смогут распространяться экспортные ограничения. О типе применённой технологии производства ничего не сообщается. Известно, что контроллер обеспечивает полную поддержку протокола NVMe 2.0. Заявленная скорость последовательного чтения достигает 14 Гбайт/с, последовательной записи — 12 Гбайт/с. Показатель IOPS при произвольных чтении и записи составляет до 3,5 и 2,5 млн соответственно. Контроллер может применяться в 16- и 18-канальной конфигурации.

Источник изображения: Yingren Technology YR S900 наделён процессором ECC третьего поколения для оптимизации кодирования и декодирования 4K LDPC. По заявлению компании, использование решения вместе с новой гибридной адаптивной функцией коррекции ошибок ECC позволяет поднять производительность памяти TLC и QLC NAND. А при работе с Kioxia XL-Flash показана задержка произвольного чтения 4K на уровне 10 мкс. Среди прочего упомянута поддержка FDP (Flexible Data Placement), SR-IOV, CMB (Controller Memory Buffer), а также различных алгоритмов шифрования.

25.09.2023 [21:13], Алексей Степин

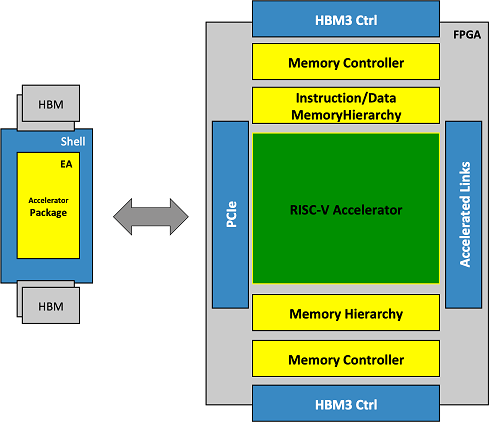

Разработка RISC-V платформы MEEP для будущих европейских суперкомпьютеров завершенаЕвропейский Союз продолжает активно развивать собственное видение суперкомпьютеров ближайшего будущего, в основу которых ляжет архитектура RISC-V. За три с половиной года работы проекта Marenostrum Experimental Exascale Platform (MEEP) создана новая платформа, детально описывающая различные блоки и свойства таких HPC-систем. Выбор микроархитектуры RISC-V в качестве основы MEEP вполне оправдан — она является открытой и позволяет разработчикам не зависеть от проприетарных наборов инструкций и аппаратных решений. Таким образом ЕС планирует достигнуть автономии в сфере супервычислений, обзаведясь собственной платформой.

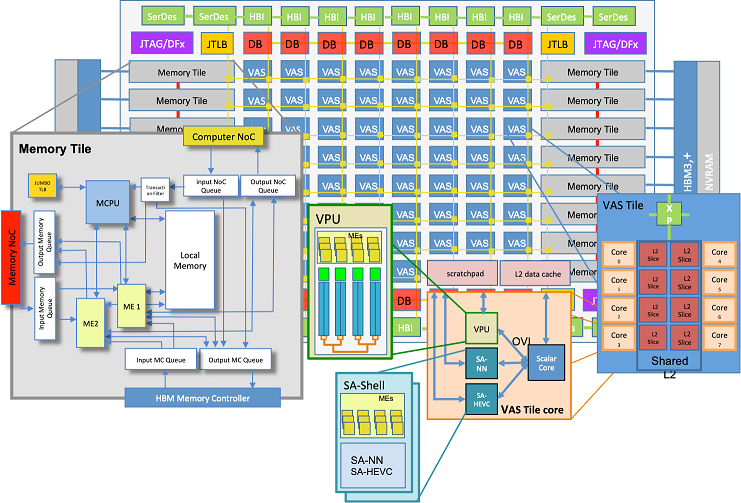

Высокоуровневое описание эмулируемого ускорителя В основе проекта MEEP лежит ядро Accelerated Memory and Compute Engine (ACME), изначально спроектированное с прицелом на применение высокоскоростной памяти HBM3 и состоящее из тайлов памяти (Memory Tile) и вычислительных тайлов VAS, объединённых меш-интерконнектом. Воплощение дизайна ACME в реальный кремний пока ещё дело будущего, но уже очевидно, что процессоры, разработанные в рамках проекта MEEP, будут иметь чиплетную компоновку.

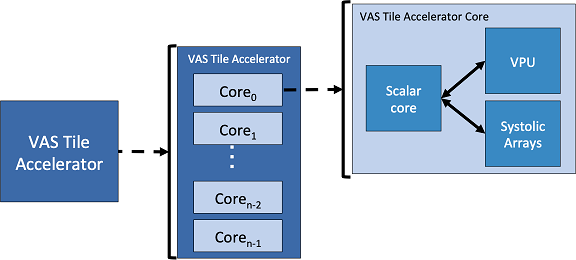

Архитектура ACME и её строительные блоки В конструкции ACME на долю Memory Tile выпадают все операции с подсистемами памяти, включая построение иерархических массивов, использующих разные типы памяти, в том числе MRAM и HBM3. Модули VAS включают себя по 8 процессорных ядер со своими разделами L2-кеша. Каждое такое ядро состоит из нескольких отдельных блоков: скалярного RISC-V, блока векторных операций, а также блоков ускорителей двух типов — SA-HEVC для обработки видео и SA-NN для нейросетевых задач, в частности, инференса.

Схема работы ускорителей в составе блоков VAS По сути, каждый модуль VAS представляет собой вполне законченный многоядерный процессор RISC-V, способный работать со всеми современными форматами данных, автоматически распознающий расширенные инструкции и выполняющий их с помощью соответствующих ускорителей в своём составе. Платформа, созданная в рамках проекта MEEP, уже функционирует как эмулируемый с помощью FPGA Xilinx полноценный прототип. Он позволяет не только вести разработку и отладку ПО для новой европейской суперкомпьютерной экосистемы, но и производить валидацию аппаратных компонентов для будущих ускорителей/процессоров с архитектурой ACME.

13.09.2023 [15:04], Сергей Карасёв

ИИ-стартап Axelera представил платформу Metis AI для периферийных вычисленийМолодая компания Axelera AI B.V. сообщила о начале поставок платформы Metis AI, разработанной специально для ускорения ИИ-задач на периферии. Стартап, основанный в 2021 году, получил финансирование на сумму более $50 млн. Чип Axelera основан на открытой архитектуре RISC-V. В базовом варианте платформа Metis AI обеспечивает производительность до 39,3 TOPS. Увеличив тактовую частоту, быстродействие можно довести до 48,16 TOPS. Изделие предлагается в различных вариантах исполнения, включая карты расширения PCIe (FHHL), модули М.2 2280 и полноценные системы для задач машинного зрения. В частности, карты PCIe AI Edge доступны в версиях с одним и несколькими чипами с общей производительностью до 856 TOPS. Утверждается, что платформа Metis AI обладает высокой энергетической эффективностью — это важно при организации ИИ-вычислений на периферии.

Источник изображений: Axelera AI B.V. Изделия Metis AI используют чипы Axelera Metis AIPU, содержащие четыре ядра для in-memory вычислений. Объём SRAM-кеша L1 составляет 16 Мбайт, кеша L2 — 32 Мбайт. Диапазон рабочих температур простирается от -40 до +85 °C. Гарантирована совместимость с Ubuntu 20.04/22.04 и Yocto. Разработчикам доступен набор инструментов Voyager SDK и фирменный компилятор TVM, который включает в себя средства оптимизации.  Модуль Axelera M.2 в формате 2280 наделён 512 Мбайт памяти LPDDR4x и одним чипом Axelera Metis AIPU. Энергоэффективность достигает 15 TOPS в расчёте на 1 Вт. Задействовано пассивное охлаждение; интерфейс подключения — PCIe 3.0 х4. Цена составляет €150. В свою очередь, карты Axelera PCIe AI Edge доступны в версиях с одним (+1 Гбайт набортной RAM) и четырьмя чипами Axelera Metis AIPU: в первом случае быстродействие достигает 214 TOPS (INT8), во втором — 856 TOPS. Устройства выполнены в виде однослотовых карт с интерфейсом PCIe 3.0 х4 и PCIe 3.0 х16. Применена система активного охлаждения с вентилятором. Цена составляет около €200 и €500 соответственно. |

|