Материалы по тегу: risc-v

|

21.02.2024 [13:46], Сергей Карасёв

RISC-V по-русски: «Микрон» начала продажи микроконтроллера «MIK32 Амур»Компания «Микрон» (входит в ГК «Элемент») сообщила о начале массовых продаж первого полностью отечественного микроконтроллера на открытой архитектуре RISC-V — изделия «MIK32 Амур». Новинка доступна у официальных дилеров и непосредственно на заводе производителя. Решение предназначено для устройств промышленной автоматизации, Интернета вещей (IoT), беспроводной периферии, интеллектуальных сетей, охранных систем, сигнализации, телеметрии, мониторинга, умного дома, управления климатом и освещением и других инфраструктурных систем. В состав «MIK32 Амур» входят ядро RISC-V, однократно программируемая память (ПЗУ на 256 бит), ОЗУ ёмкостью 16 Кбайт, а также ПЗУ (EEPROM; 8 Кбайт). Есть 12-битные АЦП и ЦАП с частотой дискретизации до 1 МГц, датчик температуры, часы реального времени с поддержкой полного календаря. Поддерживается подключаемая внешняя память программ (QSPI Flash) объёмом до 16 Мбайт. Упомянуты интерфейсы SPI, I2C, UART. Реализованы 16- и 32-разрядные таймеры с поддержкой ШИМ, захвата/сравнения сигналов. Диапазон рабочих температур простирается от -40 до +85 °C. Имеется аппаратная поддержка крипто-алгоритмов ГОСТ 34.12–2018 и AES-128.

Источник изображения: «Микрон» Среди преимуществ микроконтроллера производитель выделяет полный цикл производства в России, стабильность поставок и независимость от ограничений на импорт высокотехнологичной продукции, отсутствие зарубежной интеллектуальной собственности и минимальную стоимость среди российских аналогов. Доступна отладочная микроконтроллерная платформа на основе RISC-V. «Микроконтроллер MIK32 Амур — наша первая микросхема общепромышленного применения на архитектуре RISC-V. Тестирование и отладка успешно пройдены, микросхема в серии, и теперь MIK32 Амур доступен у всех дистрибуторов АО "Микрон", в том числе в розничной продаже — у компании "Теллур Электроникс". Действует единая матрица цен для всех дилеров АО "Микрон", основанная на объёме годовой квоты потребителя», — отмечает директор по продуктам АО «Микрон».

19.02.2024 [09:38], Сергей Карасёв

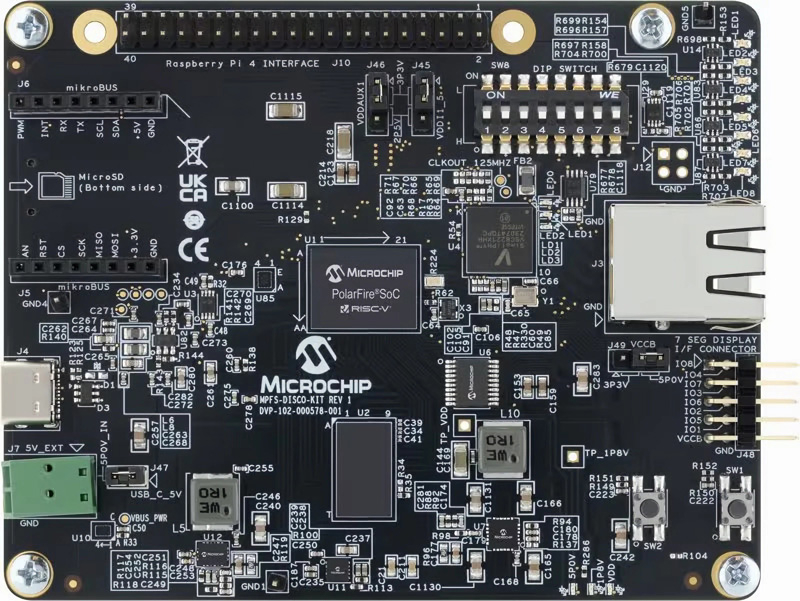

Microchip выпустила комплект PolarFire SoC Discovery Kit на базе RISC-V для приложений реального времениКомпания Microchip, по сообщению ресурса CNX-Software, начала продажи одноплатного компьютера Polarfire SoC Discovery Kit, предназначенного для разработки Linux-программ и приложений реального времени. Новинка предлагается по ориентировочной цене $130, а со скидкой по академической программе Microchip её можно приобрести за $100. В основу положена программируемая пользователем вентильная матрица (FPGA) PolarFire SoC MPFS095T-1FCSG325E с пятью ядрами на архитектуре RISC-V. Это одно ядро RV64IMAC и четыре ядра RV64GC — все они работают на тактовой частоте 625 МГц. Чип содержит четыре блока SerDes со скоростью передачи данных 12,7 Гбит/с.

Источник изображения: Microchip Изделие оснащено слотом microSD, сетевым контроллером 1GbE с разъёмом RJ-45, портом USB Type-C, коннектором mikroBUS, а также 40-контактной колодкой, совместимой с Raspberry Pi (GPIO, I2C, SPI, UART). Для вывода изображения может быть задействован интерфейс MIPI. Питание (5В / 3A) может подаваться через коннектор USB Type-C. Размеры платы составляют 104 × 84 мм. Предусмотрен встроенный программатор FlashPro5 (FP5) для настройки и отладки FPGA. Применяется софт Microchip Libero, а покупателям Polarfire SoC Discovery Kit предоставляется бесплатная лицензия Libero Silver.

09.02.2024 [23:02], Алексей Степин

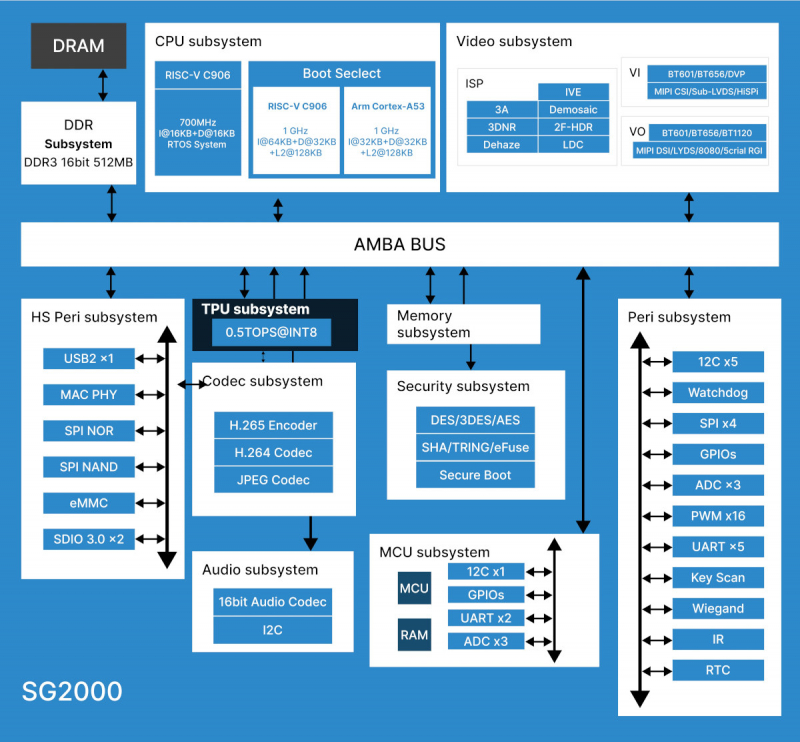

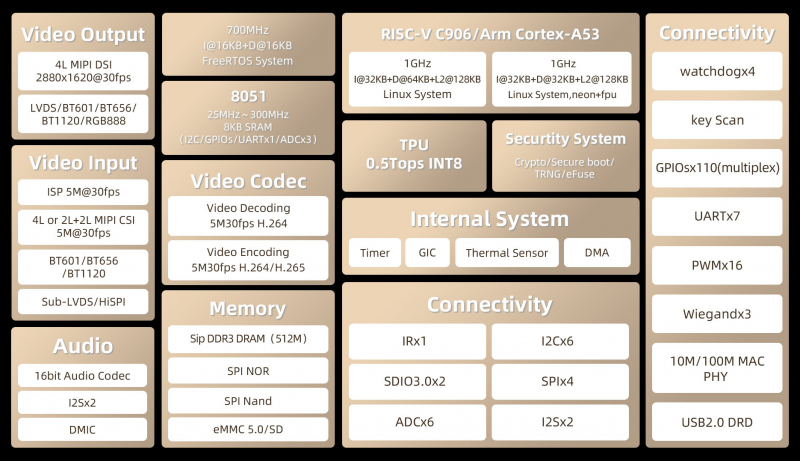

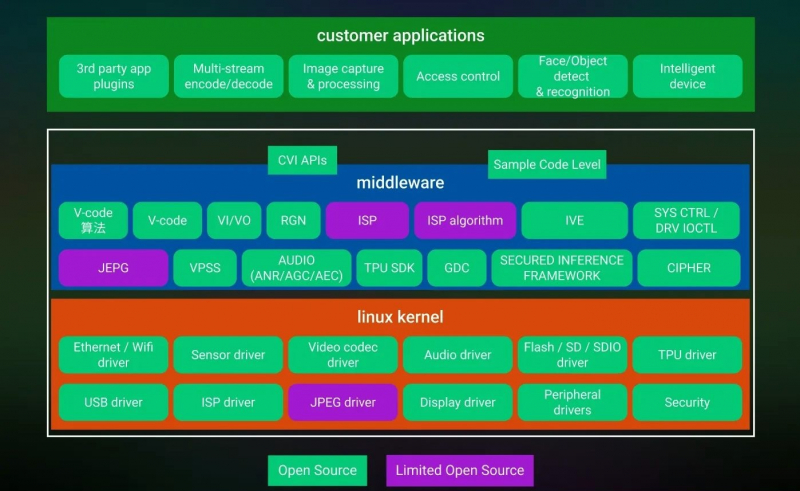

Sophgo представила гибридные SoC, сочетающие ядра Arm и RISC-VКомпания Sophgo, китайский разработчик тензорных нейрочипов и процессоров с архитектурой RISC-V, анонсировала универсальные SoC SG2000 и SG2002. Они способны работать с несколькими операционными системами одновременно, в частности, Linux, Android и FreeRTOS. Для этого разработчики снабдили новинку процессорными ядрами разных типов — RISC-V, Arm Cortex-A, Intel 8051, а также отдельным ИИ-сопроцессором. Решения предназначены для «умного интернета вещей» (Artificial Intelligence of Things, AIoT), включая «умные» IP-камеры и контроллеры систем умного дома. При этом микросхемы очень компактны, корпуса LFBGA имеют габариты всего 10 × 10 × 1,3 мм с 205 контактами. Они способны работать в диапазоне температур 0-70 °C. Архитектура новых процессоров Sophgo действительно необычна: в состав входят два 64-битных ядра RISC-V C906 с частотами 1000 и 700 МГц, одно ядро Arm Cortex-A53 с частотой 1000 МГц, а также ядро контроллера 8051 с варьирующейся от 25 до 300 МГц частотой; последнее используется для задач реального времени и имеет собственный небольшой объём SRAM. Графического ускорителя в составе новых SoC нет, однако средства обработки видеопотока имеются: блок VPU поддерживает кодирование и декодирование в форматах H.264/H.265 с разрешением 5К@30. Интегрированный NPU для работы с INT8 имеет мощность 0,5 Топс у SG2000 и 1 Топс у SG2002. Объём интегрированной оперативной памяти составляет 512 или 256 Мбайт. Подключение дисплеев реализовано через интерфейс MIPI DSI, поддерживаются разрешения вплоть до 2880 × 1620@30, имеется четыре линии MIPI CSI для подключения модулей видеокамер. Также предусмотрен 16-битный аудиокодек с двумя шинами I2S и микрофонным входом DMIC. Есть контроллеры 100 Мбит/с Ethernet и USB 2.0. Широко представлены интерфейсы для подключения различной низкоскоростной периферии: 5 × UART, 4 × SPI, 16 × PWM, 1 × IR, 6 × I2C, 6 × ADC и до 128 линий GPIO. Не забыты средства безопасности: чипы имеют собственные криптоблоки с аппаратными генераторами случайных чисел, поддерживают безопасную загрузку и располагают комплектом «пережигаемых предохранителей» (e-fuse). Разработчик заявляет о поддержке SDK на базе Linux 5.10, однако на момент анонса программные компоненты ещё не были полностью доступны. Если верить опубликованным слайдам, SDK планируется весьма развитое, включая поддержку Arduino-сред для одного из ядер RISC-V (с частотой 700 МГц). На базе новых чипов анонсировано сразу три одноплатных решения: Shenzhen MilkV Technology Duo S (SG2000) и Duo 256M (SG2002), а также Sipeed LicheeRV Nano (SG2002). Последний вариант уже доступен на Aliexpress, к нему также имеется первичная документация и репозиторий на GitHub.

05.02.2024 [13:12], Сергей Карасёв

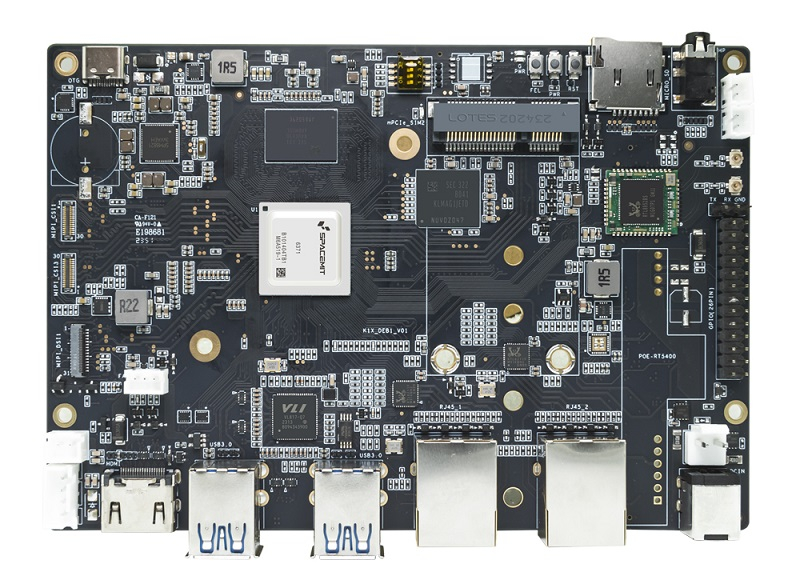

Одноплатный компьютер Banana Pi BPI-F3 оснащён процессором на базе RISC-VКоманда Banana Pi представила одноплатный компьютер BPI-F3, ориентированный на разработчиков систем промышленной автоматизации, интеллектуального производства, устройств Интернета вещей (IoT) и пр. Говорится, что изделие обеспечивает высокую производительность при небольшом энергопотреблении. Применён процессор SpacemiT K1 на архитектуре RISC-V с восемью вычислительными ядрами. Интегрированный ИИ-ускоритель обладает производительностью на уровне 2.0 TOPS. Поддерживается оперативная память LPDDR4/4X максимальным объёмом 16 Гбайт. Говорится о возможности кодирования и декодирования видеоматериалов в формате 4K.

Источник изображения: Banana Pi По имеющимся данным, быстродействие SpacemiT K1 в одноядерном режиме сравнимо с показателями Arm Cortex-A55 с тактовой частотой 1,3 ГГц. Решение может стать интересной платформой разработки для тех, кто хочет освоить архитектуру RISC-V. Реализована поддержка пяти линий PCIe 2.1. Имеются слот М.2 для SSD, порты USB 3.0 и USB 2.0, интерфейс HDMI, а также 26-контактный разъем GPIO. Одноплатный компьютер Banana Pi BPI-F3 рассчитан на работу в широком температурном диапазоне — от -40 до +85 °C. Предусмотрен двухпортовый сетевой контроллер (вероятно, 1GbE) с разъёмами RJ-45 для подключения кабелей.

04.02.2024 [21:02], Сергей Карасёв

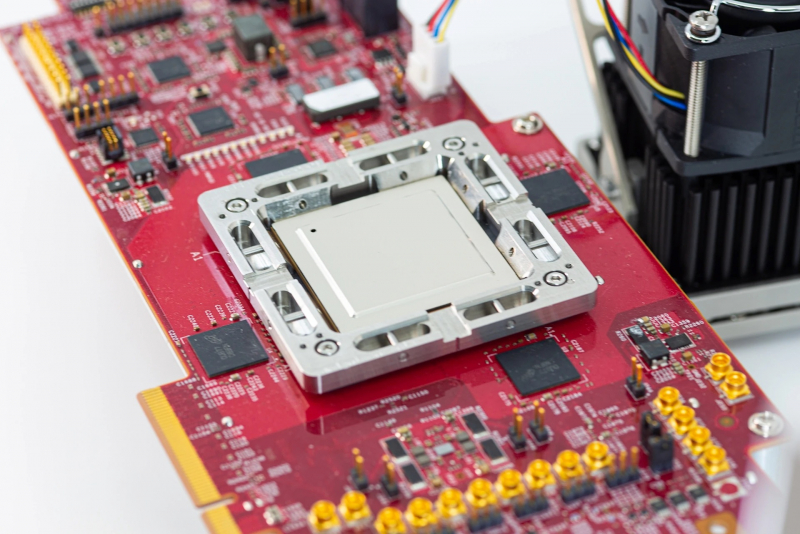

Meta✴ намерена активно внедрять собственные ИИ-ускорители Artemis в качестве альтернативы решениям NVIDIA и AMDВ 2024 году компания Meta✴, по сообщению The Register, после многих лет разработки может начать массовое внедрение собственных ИИ-чипов. Они станут альтернативой ускорителям NVIDIA и AMD, что поможет снизить зависимость от продукции сторонних поставщиков. В 2024 году компания намерена потратить до $37 млрд на развитие своей инфраструктуры. В настоящее время для поддержания ИИ-нагрузок Meta✴ применяет такие решения, как NVIDIA H100. Ожидается, что к концу 2024 года компания будет иметь в своём распоряжении 350 тыс. этих ускорителей. Вместе с тем Meta✴ проявляет интерес и к изделиям AMD Instinct MI300. Ранее компания высоко оценила возможности Qualcomm Cloud AI 100, но отказалась от них из-за несовершенства ПО. Не приглянулись Meta✴ и чипы Esperanto. Сейчас Meta✴ ведёт разработку собственных ИИ-ускорителей.

Источник изображения: Meta✴ Весной 2023 года стало известно, что компания создала свой первый ИИ-процессор. Чип под названием MTIA (Meta✴ Training and Inference Accelerator; на изображении) представляет собой ASIC в виде набора блоков, функционирующих в параллельном режиме. Задействованы 64 вычислительных элемента в виде матрицы 8 × 8, каждый из которых объединяет два ядра с архитектурой RISC-V. Конструкция включает 128 Мбайт памяти SRAM, а также до 64/128 Гбайт памяти LPDDR5. Показатель TDP равен 25 Вт. Заявленная производительность на операциях INT8 достигает 102,4 TOPS, на операциях FP16 — 51,2 Тфлопс. Процессор производится по 7-нм технологии TSMC.

Источник изображения: Meta✴ Как теперь сообщается, в 2024-м Meta✴ намерена начать активное использование собственных ИИ-ускорителей с кодовым именем Artemis. В их основу лягут компоненты MTIA первого поколения. Чип Artemis, оптимизированный для инференса, будет применяться наряду с ускорителями сторонних поставщиков. При этом, как отметили представители компании, изделия Artemis обеспечат «оптимальное сочетание производительности и эффективности при рабочих нагрузках, специфичных для Meta✴».

Источник изображения: Meta✴ Компания пока не раскрывает ни архитектуру Artemis, ни конкретные рабочие нагрузки, которые будет поддерживать чип. Участники рынка полагают, что Meta✴ будет запускать готовые ИИ-модели на собственных специализированных ASIC, чтобы высвободить ресурсы ускорителей для развивающихся приложений. По данным SemiAnalysis, Artemis получит улучшенные ядра, а компоненты LPDDR5 уступят место более быстрой памяти, использующей технологию TSMC CoWoS. Нужно добавить, что Amazon и Google уже несколько лет используют собственные чипы для ИИ-задач. Например, Amazon недавно ИИ-ускорители Trainium2 и Inferenetia2, тогда как Google в 2023 году представила сразу два новых ускорителя: Cloud TPU v5p и TPU v5e. А Microsoft сообщила о создании ИИ-ускорителя Maia 100.

25.01.2024 [18:15], Сергей Карасёв

Китайская Sophgo хочет поставлять в Россию тензорные ИИ-процессорыКитайский разработчик тензорных процессоров Sophgo, по информации газеты «Коммерсантъ», намерен организовать поставку своих решений российским производителям вычислительной техники. Такие изделия могут заинтересовать компании, реализующие проекты в области нейросетей и ИИ. Sophgo занимается созданием специализированных чипов SOPHON с архитектурой RISC-V и Arm. В частности, в ассортименте компании присутствует 16-ядерное изделие SG2380 со встроенным ИИ-ускорителем. Еще одна разработка — тензорный процессор BM1684X, который обеспечивает быстродействие до 32 TOPS на операциях INT8, до 16 Тфлопс при вычислениях FP16/BF16 и до 2 Тфлопс на операциях FP32.

Источник изображения: Sophgo По имеющимся сведениям, Sophgo хочет официально поставлять в Россию тензорные процессоры для нейронных сетей, а также CPU собственной разработки на основе RISC-V. Предполагается, что эти изделия будут применяться в том числе в серверах. Однако участники российского рынка смотрят на инициативу Sophgo скептически, передаёт «Коммерсантъ». Для использования чипов Sophgo российским производителям придётся с нуля разрабатывать совместимые компоненты, на что потребуется минимум два года и несколько миллиардов рублей инвестиций. Кроме того, решения Sophgo ориентированы прежде всего на микросерверы и сетевое оборудование. В России в такой электронике используются процессоры на базе x86 и Arm, которые уже имеют развитую экосистему. В октябре 2023 года стало известно, что российская компания «Норси-Транс» организует выпуск серверов, СХД, настольных компьютеров и ноутбуков на процессорах другой китайской компании — Loongson. Эксперты говорят, что это может создать зависимость отечественной электроники от китайской продукции. Соответствующий риск актуален и для тензорных чипов.

24.12.2023 [14:13], Сергей Карасёв

Пять известных компаний учредили фирму Quintauris для ускорения внедрения RISC-VКомпании Robert Bosch GmbH, Infineon Technologies AG, Nordic Semiconductor ASA, NXP Semiconductors и Qualcomm Technologies официально объявили о формировании совместного предприятия Quintauris GmbH. Главной задачей этой фирмы, базирующейся в Мюнхене (Германия), является развитие экосистемы RISC-V. Перечисленные игроки рынка сообщили об объединении усилий с целью разработки и продвижения продуктов на открытой процессорной архитектуре RISC-V в августе уходящего года. Тогда говорилось, что участники проекта намерены сфокусироваться на решениях для автомобильной промышленности, а в дальнейшем расширить деятельность, охватив продукты для Интернета вещей (IoT) и мобильные устройства.

Источник изображения: Quintauris Сообщается, что работы в рамках проекта будут вестись через Quintauris. Генеральным директором этого предприятия назначен Александр Кохер (Alexander Kocher). Ранее он занимал пост президента и гендиректора Elektrobit — поставщика специализированного софта для автомобильной промышленности. До прихода в Elektrobit Кохер был вице-президентом и главой автомобильного подразделения Wind River. На сайте Quintauris говорится, что фирма создана для обеспечения совместимости продуктов на базе RISC-V, предоставления эталонных архитектур и помощи в создании решений для различных отраслей. Все необходимые разрешения со стороны регулирующих органов для формирования Quintauris уже получены. Предприятие учреждено 22 декабря 2023 года; об объёме инвестиций в проект ничего не говорится.

30.11.2023 [14:18], Сергей Карасёв

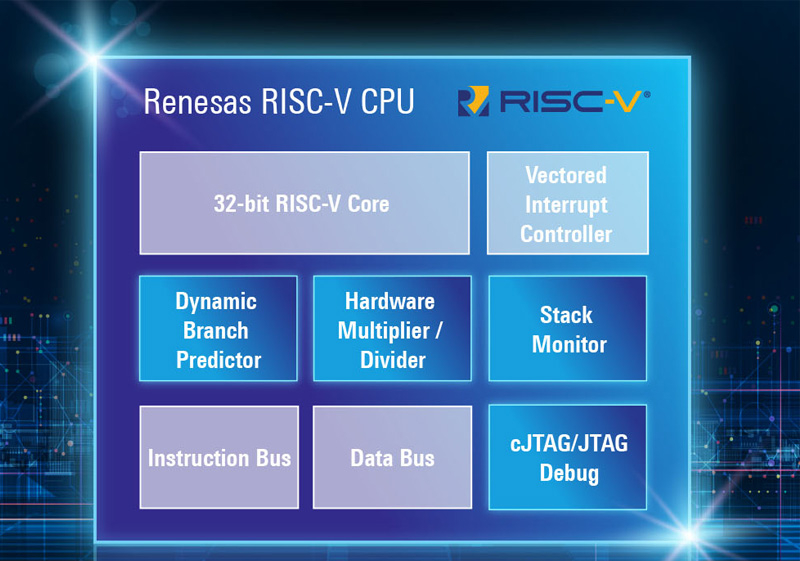

Renesas представила собственное 32-бит ядро RISC-VКомпания Renesas Electronics объявила о создании собственного 32-битного процессорного ядра на основе архитектуры набора команд RISC-V (ISA) с открытым исходным кодом. Решение дополнит существующее семейство 32-бит микроконтроллеров (MCU) Renesas, включая проприетарные изделия RX и RA на архитектуре Arm Cortex-M. RISC-V-ядро Renesas предназначено для создания чипов общего назначения. Предполагается, что такие процессоры найдут применение в устройствах Интернета вещей, потребительской электронике, медицинском оборудовании, индустриальных системах и пр.

Источник изображения: Renesas Новое ядро может выполнять функции основного контроллера приложений или дополнительного вторичного узла в SoC. Кроме того, ядро подходит для применения в составе внутрикристальных подсистем и специализированных изделий (ASSP). Производительность оценивается в 3,27 CoreMark/МГц, что, как утверждает Renesas, превосходит показатель других сопоставимых по классу решений, представленных на рынке. В ядре Renesas реализованы некоторые расширения RISC-V ISA: это M (целочисленное умножение/деление), А (атомарные операции с памятью), С (сжатый формат команд; подмножество RV32I) и В (инструкции для манипуляций с битами). Компания Renesas планирует выпустить свой первый MCU на базе RISC-V и соответствующие инструменты разработки в I квартале 2024 года. Тогда же будут обнародованы технические подробности о продукте.

13.11.2023 [13:56], Сергей Карасёв

Synopsys представила ядра ARC-V на архитектуре RISC-VКомпания Synopsys анонсировала процессорные ядра ARC-V на архитектуре RISC-V, которые будут доступны для лицензирования сторонним разработчикам. Заказчики смогут воспользоваться сопутствующими инструментами, включая средства автоматизации проектирования электронных устройств на базе ИИ Synopsys.ai. В семейство Synopsys ARC-V Processor IP вошли модификации с высоким и средним уровнями производительности, а также версия со сверхнизким энергопотреблением. Разработчики смогут воспользоваться платформой Synopsys MetaWare для создания эффективного и высокооптимизированного кода.

Источник изображения: Synopsys Кроме того, анонсировано ядро Synopsys ARC-V Functional Safety (FS) со встроенными аппаратными функциями безопасности для обнаружения системных ошибок. Говорится об уровнях безопасности ASIL B и ASIL D. Изделие разработано на основе системы управления качеством (QMS) Synopsys, сертифицированной по стандарту ISO 9001. А пакет MetaWare Development Toolkit for Safety поможет разработчикам ускорить написание кода, соответствующего стандарту ISO 26262. 32-битное ядро Synopsys ARC-V RMX для встраиваемых систем станет доступно во II квартале 2024 года. 32-битное ядро реального времени Synopsys ARC-V RHX и 64-битное ядро Synopsys ARC-V RPX IP планируется выпустить во второй половине следующего года. Synopsys также сообщила, что её представитель войдёт в состав совета директоров и технический руководящий комитет некоммерческой организации RISC-V International, которая занимается координацией разработки данной архитектуры.

09.11.2023 [14:56], Сергей Карасёв

Китай развернул первый облачный кластер на базе RISC-VШаньдунский университет в Китае, по сообщению HPC Wire, развернул в облаке первый коммерческий кластер с серверами, оснащёнными процессорами на открытой архитектуре RISC-V. Это очередная попытка КНР сократить зависимость от зарубежных технологий в свете возрастающего санкционного давления со стороны США. В составе запущенной платформы задействованы процессоры Sophgo SOPHON SG2042 с 64 ядрами RISC-V и 64 Мбайт кеша L3. Тактовая частота достигает 2,0 ГГц. Реализована поддержка интерфейса PCIe Gen 4. В составе системы в общей сложности объединены 48 узлов, что в сумме даёт 3072 ядра. Система, как отмечается, предназначена прежде всего для учебных и исследовательских целей. Однако она также поддерживает работу определённых облачных инстансов.

Источник: RISC-V Summit У Китая есть комплексный план по разработке собственных чипов RISC-V. В этом году Министерство науки и технологий КНР профинансировало разработку таких чипов, и многие университеты и научные лаборатории также подключились к созданию таких изделий. В мае Китайская академия наук представила 2-ГГц процессор Xiangshan на архитектуре RISC-V, тогда как ведущие китайские RISC-V-разработчики сформировали патентный альянс. Говорится, что ведётся разработка изделия Xiangshan-v3: в проекте принимают участие крупные китайские компании, включая Alibaba, Tencent и ZTE. По производительности новый чип будет сопоставим с Arm Neoverse-N2. Ранее говорилось, что американские санкции против Китая могут ускорить распространение архитектуры RISC-V. Вместе с тем высказываются опасения, что запуск Пекином облачного RISC-V-кластера может привлечь дополнительное внимание со стороны регуляторов США. Законодатели в Палате представителей призвали запретить американским компаниям работать с китайскими организациями над технологиями RISC-V. |

|