Материалы по тегу: risc-v

|

23.04.2024 [11:45], Сергей Карасёв

Samsung откроет в Кремниевой долине лабораторию по созданию ИИ-чипов на базе RISC-V, чтобы побороться с NVIDIAКомпания Samsung Electronics, по сообщению ресурса Business Korea, откроет новую научно-исследовательскую и опытно-конструкторскую (R&D) лабораторию в Кремниевой долине. Её специалисты займутся прежде всего созданием ИИ-чипов на открытой архитектуре RISC-V. По имеющейся информации, Технологический институт Samsung SAIT (Samsung Advanced Institute of Technology) учредил исследовательский центр Advanced Processor Lab (APL). Южнокорейская компания намерена расширить свои возможности в области разработки ИИ-решений, чтобы в перспективе бросить вызов американским корпорациям, в числе которых называется NVIDIA. Около месяца назад Samsung сформировала лабораторию Semiconductor AGI Computing Lab, сотрудники которой разрабатывают чипы следующего поколения для ИИ-приложений. Офисы данного подразделения располагаются в Южной Корее и США. Основным направлением исследований являются системы «общего искусственного интеллекта» (Artificial General Intelligence, AGI). В заявлении в LinkedIn глава Samsung Semiconductor Ке Хён Гён (Kye Hyun Kyung) отметил, что на первом этапе лаборатория сосредоточит усилия на разработке чипов для больших языковых моделей (LLM), тогда как реализация проектов в области AGI начнётся позднее.

Источник изображения: pixabay.com Между тем власти США в рамках «Закона о чипах» выделили Samsung $6,4 млрд безвозвратных субсидий на строительство предприятий в Техасе. По условиям соглашения, в городе Тейлоре будут построены два завода по выпуску полупроводниковых изделий с нормами 4 и 2 нм. «Мы считаем, что полупроводниковые технологии нового поколения, созданные с использованием ИИ и компьютерной техники, сыграют ключевую роль в повышении качества жизни. Именно поэтому SAIT тесно сотрудничает с учёными и экспертами в поисках новых долгосрочных драйверов роста для Samsung», — говорит Гёйонг Джин (Gyoyoung Jin), президент SAIT.

20.04.2024 [20:37], Сергей Карасёв

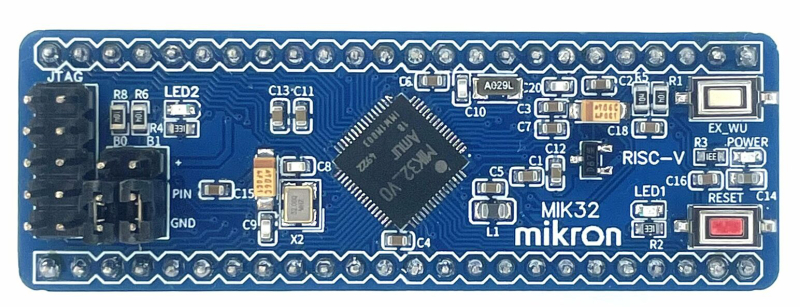

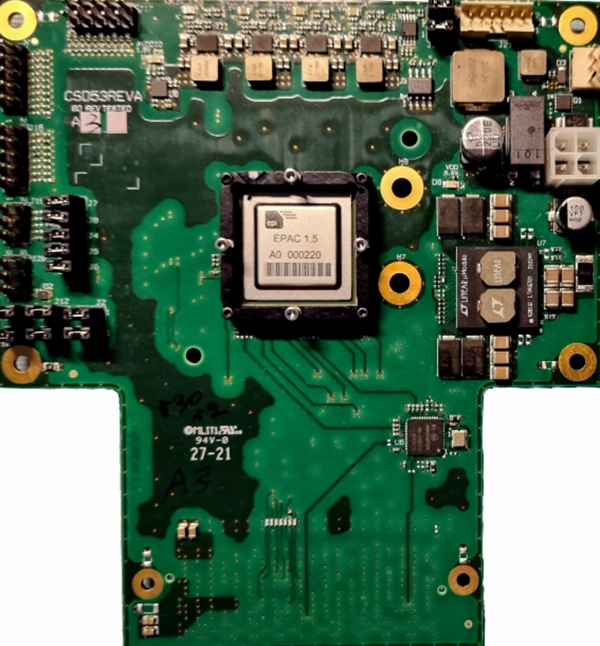

«Микрон» представил российский ПЛК на базе RISC-V для автоматизации критических инфраструктурКомпания «Микрон» (входит в ГК «Элемент») представила прототип первого в России программируемого логического контроллера (ПЛК) на базе «MIK32 Амур» с открытой архитектурой RISC-V. Новинка предназначена для автоматизации критических инфраструктур. Изделие «MIK32 Амур» содержит ядро RISC-V, однократно программируемую память (ПЗУ на 256 бит), ОЗУ ёмкостью 16 Кбайт, а также ПЗУ (EEPROM; 8 Кбайт). Предусмотрены 12-битные АЦП и ЦАП с частотой дискретизации до 1 МГц, датчик температуры, часы реального времени с поддержкой полного календаря. Новый ПЛК, как утверждается, ориентирован прежде всего на те сферы, где требуется обеспечение бесперебойной работы оборудования. Это топливно-энергетические инфраструктуры, светотехника, охранные системы, решения для сектора машиностроения, системы водоснабжения и пр. Изделие обладает следующими техническими характеристиками:

Говорится, что новая разработка снижает зависимость от импортных компонентов и предоставляет возможность в короткие сроки обеспечить российским защищённым решением объекты критической инфраструктуры. Сроки начала массовых поставок изделия не уточняются.

18.04.2024 [12:20], Сергей Карасёв

Rivos, разработчик ИИ-ускорителей на базе RISC-V, получил на развитие более $250 млнКалифорнийский стартап Rivos, основанный в 2021 году, сообщил о проведении раунда финансирования Series-A3, в ходе которого на развитие привлечено более $250 млн. Ключевым инвестором стала фирма Matrix Capital Management. Кроме того, средства предоставили Intel Capital, Dell Technologies Capital, MediaTek и др. Rivos занимается разработкой чипов на открытой архитектуре RISC-V для приложений ИИ и больших языковых моделей (LLM). Изделия планируется изготавливать на предприятии TSMC с применением 3-нм технологии. Предполагается, что такие решения станут менее дорогой альтернативой ускорителям NVIDIA. Привлеченные средства стартап направит на ускорение разработки чипов и коммерциализацию решений. При этом ориентировочные сроки начала массового производства таких изделий пока не раскрываются.

Источник изображения: pixabay.com На сегодняшний день Rivos раскрывает лишь общую информацию о характеристиках своих чипов. В их состав войдёт узел Data Parallel Accelerator и вычислительные ядра с архитектурой RISC-V. Узлы чипа получат доступ к памяти DDR DRAM и HBM. Rivos также предоставит набор специальных программных инструментов для своих чипов. С их помощью разработчики смогут развёртывать и обучать модели ИИ. По имеющейся информации, Rivos нацеливается на приложения ИИ, которые смогут работать с PyTorch и JAX.

16.04.2024 [15:20], Сергей Карасёв

Испания и Бразилия займутся совместными разработками чипов RISC-V для HPC и ИИБарселонский суперкомпьютерный центр (Centro Nacional de Supercomputación, BSC-CNS) и бразильский институт Эльдорадо (Instituto Eldorado) объявили о заключении соглашения о сотрудничестве в области процессоров с открытой архитектурой RISC-V. Основная цель проекта — развитие направлений НРС и ИИ. Стороны намерены заняться совместной разработкой специализированного блока ускорения матричного умножения, который в перспективе планируется интегрировать в чипы RISC-V. В рамках соглашения о сотрудничестве BSC-CNS и институт Эльдорадо подписали меморандум о взаимопонимании. О размере инвестиций в проект пока ничего не сообщается. Но отмечается, что инициатива является частью Приоритетной программы национальных интересов Бразилии (PPI-Softex) и осуществляется при поддержке Министерства науки, технологий и инноваций страны. Речь идёт об установлении технологического партнёрства между Бразилией и Европейским союзом, укреплении обмена знаниями, а также о поддержке передовых исследований и разработок.

Источник изображения: BSC-CNS BSC-CNS и институт Эльдорадо намерены выполнять работы в сотрудничестве со специалистами Университета Кампинаса (UNICAMP) в штате Сан-Паулу (Бразилия). Ожидается, что в перспективе чипы с архитектурой RISC-V произведут революцию в области НРС. Новое партнёрство призвано ускорить внедрение инноваций в соответствующей области. Стоит отметить, что недавно центр BSC-CNS заключил многолетнее соглашение о сотрудничестве с NVIDIA. Этот проект нацелен на разработку инновационных решений, объединяющих технологии НРС и ИИ. Стороны, в частности, займутся созданием больших языковых моделей (LLM).

09.04.2024 [15:11], Сергей Карасёв

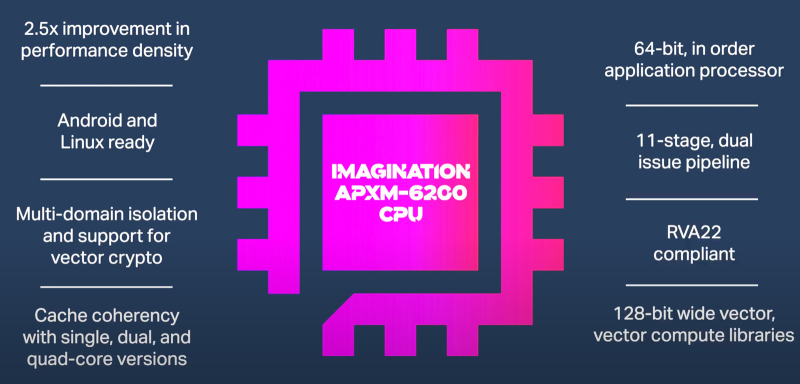

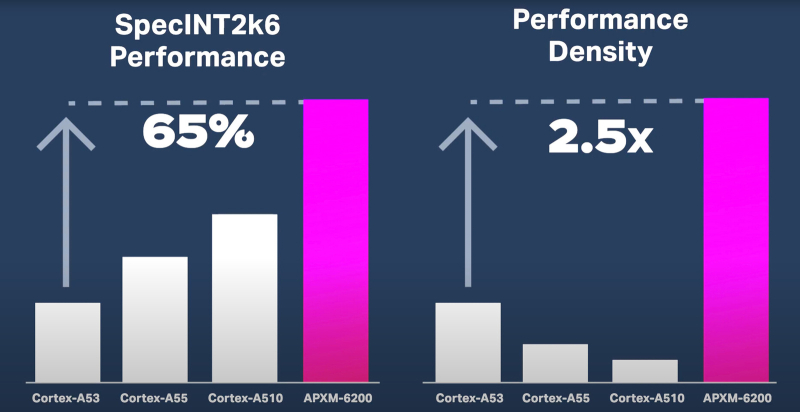

Imagination представила RISC-V процессор APXM-6200 для интеллектуальных устройствКомпания Imagination Technologies анонсировала новый продукт в семействе Catapult CPU — процессор приложений APXM-6200 с открытой архитектурой RISC-V. Ожидается, что новинка найдёт применение в интеллектуальных, потребительских и промышленных устройствах. APXM-6200 — это 64-бит процессор без внеочередного выполнения инструкций. Изделие использует 11-стадийный конвейер с возможностью одновременной обработки двух инструкций. Чип может содержать одно, два или четыре вычислительных ядра. Под заказ также будут доступны варианты с 8 и 12 ядрами. Объём кеша L1 составляет до 128 Кбайт, L2 — 1 Мбайт на ядро (кеш L3 не предусмотрен). Imagination утверждает, что по сравнению с сопоставимыми по классу процессорами, уже представленными на рынке, чип APXM-6200 обеспечивает повышение производительности на 65 % и увеличение плотности производительности в 2,5 раза. Реализована поддержка векторных расширений и различных средств обеспечения безопасности. Говорится о совместимости с Linux и Android. В целом, как утверждается, новинка сочетает в себе высокую производительность при низком энергопотреблении и ИИ-функциональности. Изделие APXM-6200 подходит для устройств умного дома (смарт-телевизоры, телеприставки и пр.), носимых гаджетов, оборудования промышленного Интернета вещей, логических и сетевых контроллеров и др. Разработчикам техники на базе RISC-V компания Imagination предлагает комплект Catapult SDK. Отмечается, что количество устройств на базе RISC-V стремительно растёт: по прогнозам, к 2030 году их будет более 16 млрд. Причём основную часть составят продукты для потребительского рынка. Ожидается, что к концу текущего десятилетия пятая часть всех потребительских устройств будет оснащена процессором на базе RISC-V.

09.04.2024 [12:57], Сергей Карасёв

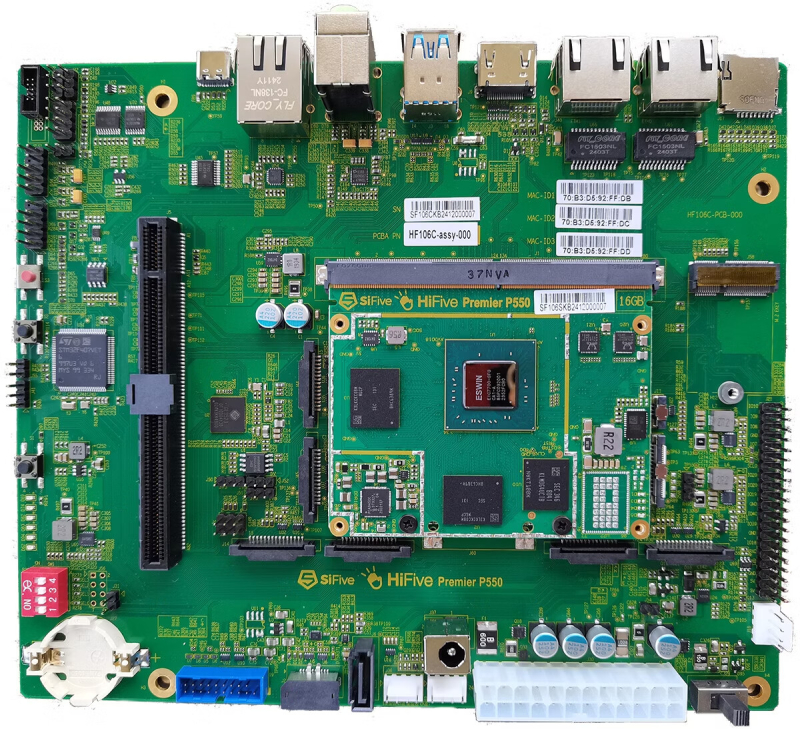

SiFive представила RISC-V платформу для разработчиков HiFive Premier P550Компания SiFive представила платформу для разработчиков HiFive Premier P550 на архитектуре RISC-V. Новинка подходит для проектов, связанных с машинным зрением, видеоанализом, ИИ и пр. В основу решения положена «система на чипе» Eswin EIC7700 SoC с четырьмя вычислительными ядрами SiFive Performance P550 с внеочередным выполнением инструкций. Объём кеша L2 составляет 256 Кбайт, кеша L3 — 4 Мбайт. В состав SoC входят графический блок 2D/3D GPU, аппаратный модуль кодирования/декодирования видео, нейропроцессорный движок (NPU), контроллер памяти DDR5 и пр. Отмечается, что новинка обеспечивает ИИ-производительность до 13,3 TOPS. Возможна обработка видеоматериалов формата 8K@50 или 28 каналов 1080р@30. В зависимости от модификации плата несёт на борту 16 или 32 Гбайт оперативной памяти LPDDR5. Вместимость флеш-модуля eMMC составляет 128 Гбайт. В оснащение включены два сетевых порта 1GbE, порт SATA-3, слот PCIe 3.0 х16, пять портов USB 3.2 Gen1, коннектор M.2 E-Key (PCIe 3.0) для комбинированного адаптера Wi-Fi/Bluetooth. Решение выполнено в формате miniDTX с габаритами 203 × 170 мм. Ожидается, что HiFive Premier P550 поступит в продажу на платформе Arrow Electronics в июле 2024 года. Говорится о совместимости с Linux — при создании новинки SiFive сотрудничала с компанией Canonical, отвечающей за развитие Ubuntu. SiFive называет новинку самой высокопроизводительной на сегодняшний день платой на базе RISC-V для разработчиков.

22.03.2024 [23:59], Руслан Авдеев

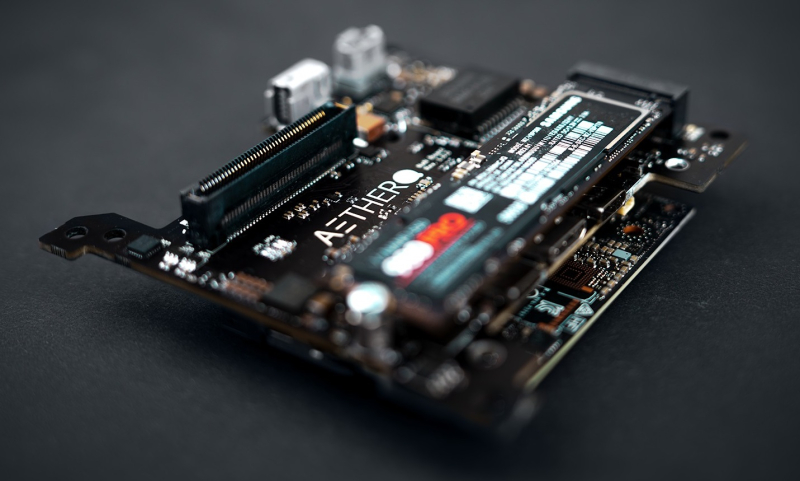

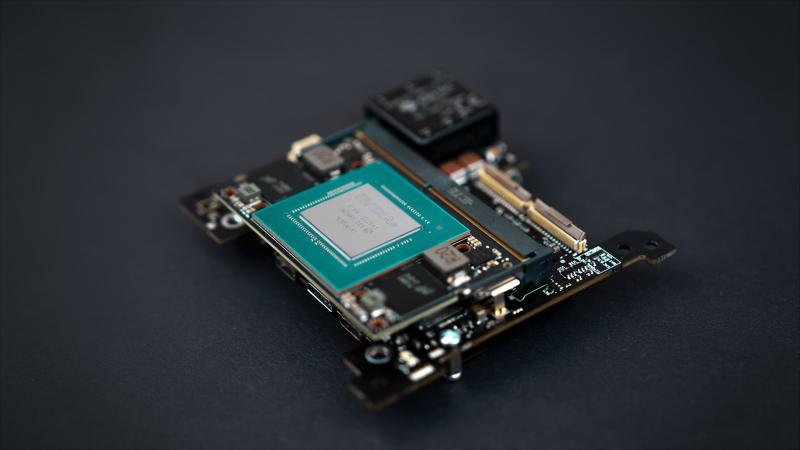

Aethero намерена стать «Intel или NVIDIA в космической индустрии», разработав защищённые ИИ-платформы для спутников и станцийХотя сенсоры многочисленных орбитальных спутников собирают немало информации, у космических аппаратов не хватает вычислительных способностей, чтобы обрабатывать данные на месте. TechCrunch сообщает, что стартап Aethero намерен стать «Intel или NVIDIA в космической индустрии» — компания разрабатывает защищённые от радиации компьютеры для периферийных вычислений на спутниках. Несколько лет назад основатели Aethero создали стартап Stratodyne, занимавшийся строительством стратостатов для дистанционного зондирования (ДЗЗ). Позже компания закрылась, а создатели вернулись к изучению встраиваемых систем для агрессивных сред. Как заявляет Aethero, современные компьютеры для космоса используют устаревшие FPGA и не способны выполнять сложные вычисления вроде тренировки на орбите ИИ-моделей или обслуживания систем компьютерного зрения. Aethero, привлёкшая $1,7 млн, намерена только в этому году трижды отправить свои разработки в космос. Одна из миссий будет выполнена SpaceX уже в июне. Целью является демонстрация работоспособности прототипов вроде возможности обновления набортных моделей компьютерного зрения или тренировки таких моделей непосредственно в космосе на собранных здесь же данных. Космический компьютер первого поколения ECM-NxN использует чип NVIDIA Jetson Orin Nano. В компании утверждают, что сегодня это лучший периферийный ИИ-ускоритель на рынке, а надёжное оборудование собственной разработки позволит сохранить его работоспособность на низкой околоземной орбите в течение 7–10 лет. При этом платформа уместится даже в небольшом аппарате вроде кубсата и обеспечивает производительность в 20 раз выше в сравнении с уже существующими решениями. Впоследствии Aethero намерена выпустить более крупный модуль ECM-NxA на базе NVIDIA AGX, а потом перейти к разработке собственного RISC-V чипа для модуля ECM-0x1. Утверждается, что тот будет потреблять меньше энергии и будет производительнее, чем продукты техногигантов. Выпуск планируется совместно с Intel приблизительно в 2026 году, хотя обстоятельства могут измениться. В Aethero отмечает, что подобные решения могут быть интересны операторам ДЗЗ, орбитальным сервисам и будущим частным космическим станциям. Например, только МКС генерирует терабайты данных ежедневно, напоминает компания. Правда, на МКС работает уже второе поколение космического суперкомпьютера HPE Spaceborne-2, разработчики которого отмечали проблемы с SSD и кешами процессоров из-за радиации. На МКС была протестирована и edge-платформа AWS Snowcone. Более того, ИИ-софт AWS для анализа снимков уже успел поработать на низкоорбитальном спутнике.

21.03.2024 [13:29], Сергей Карасёв

Alibaba в 2024 году выпустит серверный процессор на архитектуре RISC-VDamo Academy, исследовательское подразделение Alibaba, по сообщению ресурса The Register, проектирует процессор «серверного класса» на открытой архитектуре RISC-V. Чип с обозначением C930, как ожидается, дебютирует в текущем году. Появление подобных изделий имеет большое значение для Китая в связи с жёсткими санкциями со стороны США, которые закрыли для местных компаний доступ к технологиям производства передовых микропроцессоров. Alibaba достаточно продолжительное время ведёт исследования и разработки в области RISC-V. Так, ещё в 2019 году компания анонсировала 16-ядерный процессор XT 910 на этой архитектуре для «умной» периферии и edge-платформ. А в 2022-м фирма T-Head, одно из подразделений Alibaba Group, представила платформу Wujian 600 для разработки SoC на базе RISC-V. Она легла в основу изделия TH1520, ключевым компонентом которого является процессор XuanTie C910 с четырьмя вычислительными ядрами RISC-V.

Источник изображения: Alibaba Подробности о готовящемся чипе C930 пока не раскрываются. При этом специалисты Damo Academy обсуждали новый портативный компьютер RuyiBOOK, оснащённый упомянутым процессором C910. Ранее этот чип использовался в некоторых одноплатных компьютерах, таких как Lichee Module 4 Model A. Любопытно, что на ноутбуке применяется ОС openEuler, основанная на наработках коммерческого дистрибутива EulerOS, который изначально был построен на базе CentOS. Можно предположить, что RuyiBOOK ориентирован прежде всего на коммерческий сектор. Ожидается, что процессор C930 будет использоваться в серверах, предназначенных в том числе для работы с ИИ-приложениями. Однако пока не ясно, планирует ли Alibaba применять новый чип в оборудовании для своих облачных платформ. Так или иначе, создание собственных решений на основе RISC-V поможет Alibaba снизить зависимость от зарубежных изделий. Нужно также отметить, что ранее упомянутое подразделение T-Head, а также другие китайские RISC-V-разработчики, включая Xinlai Technology, Shanghai Saifang Technology, Juquan Optoelectronics, Xinsiyuan Microelectronics и StarFive, сформировали патентный альянс. Цель проекта — создать «здоровую экосистему чипов с открытым кодом и способствовать быстрому развитию платформы RISC-V». Китайская академия наук в 2023 году представила новый RISC-V процессор семейства Xiangshan, а у SOPHGO имеются 64-ядерные CPU на той же архитектуре и серверные решения на их основе.

15.03.2024 [22:43], Алексей Степин

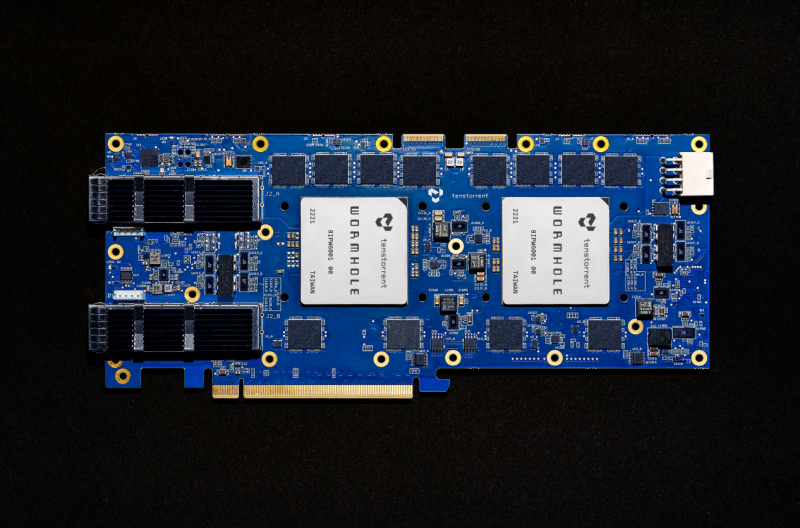

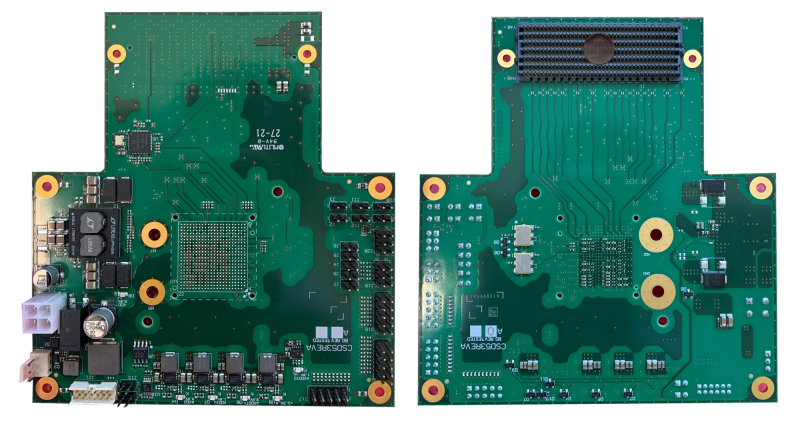

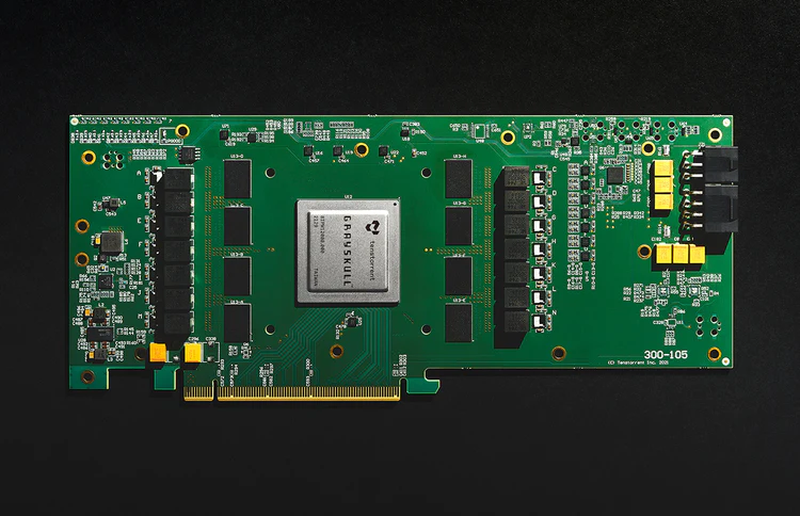

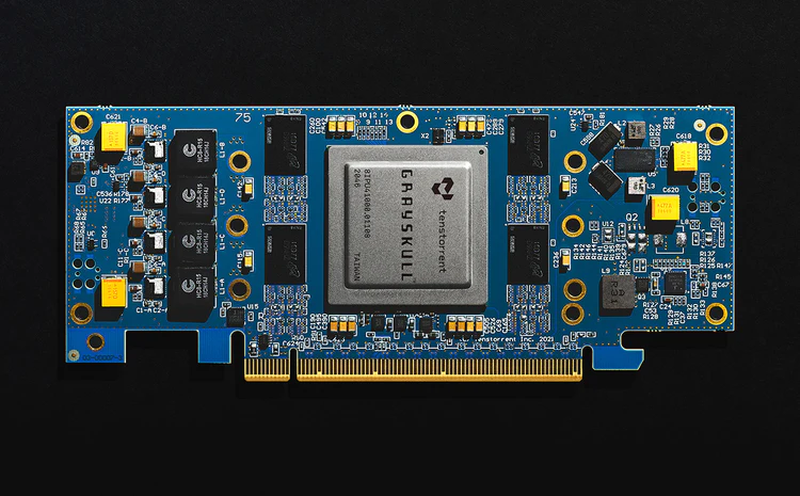

Tenstorrent под руководством Джима Келлера представила свои первые ИИ-ускорители Grayskull на базе RISC-VКанадский разработчик микрочипов Tenstorrent, возглавляемый легендарным Джимом Келлером (Jim Keller), наконец, представил свои первые решения на базе архитектуры RISC-V — ИИ-процессоры Grayskull и ускорители на их основе, Grayskull e75 и e150. Оба варианта доступны для приобретения уже сейчас по цене $599 за младшую версию и $799 за старшую. Данные решения предназначены для инференс-систем, разработки и отладки ПО. В комплект разработчика входят инструменты TT-Buda и TT-Metalium. В первом случае речь идёт о высокоуровневом стеке, предназначенном для компиляции и запуска ИИ-моделей на аппаратном обеспечении Tenstorrent, а во втором — о низкоуровневой программной платформе, обеспечивающей прямой доступ к аппаратным ресурсам. Поддерживается PyTorch, ONNX и другие фреймворки. Создатели делают особенный упор на простоте программирования в сравнении с классическими GPU. Поддерживается широкий спектр ИИ-моделей, но Tenstorrent особенно выделяет BERT, ResNet, Whisper, YOLOv5 и U-Net.

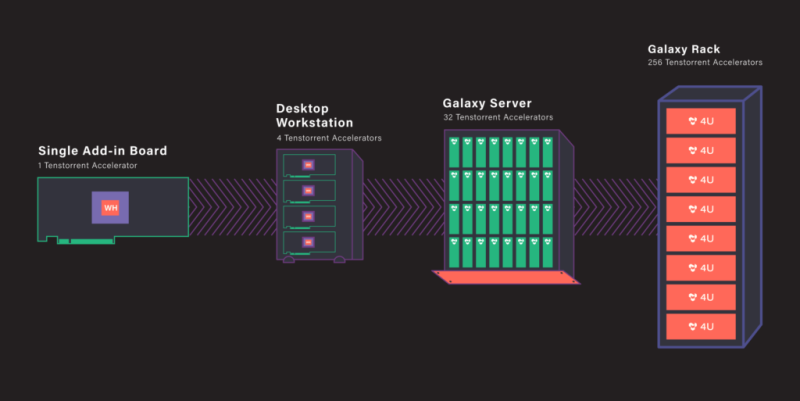

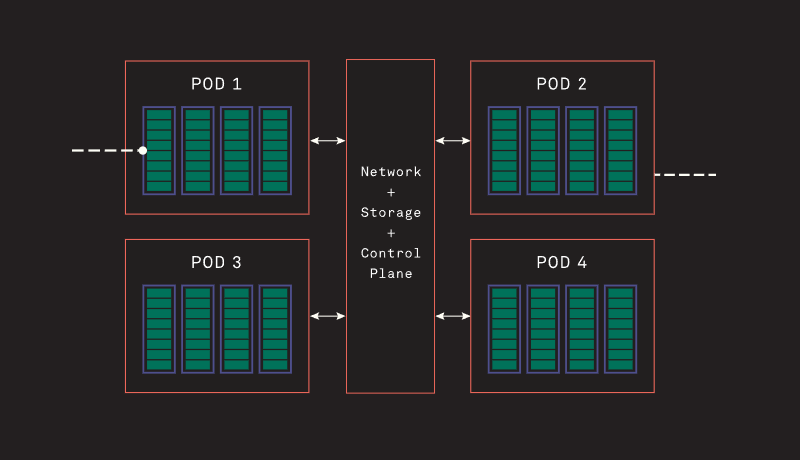

Источник изображений здесь и далее: Tenstorrent Архитектура Grayskull базируется на RISC-V, в настоящий момент максимальное количество фирменных ядер Tensix достигает 120, работают они на частотах вплоть до 1,2 ГГц. Каждое такое ядро содержит пять полноценных ядер RISC-V, блок тензорных операций, блок SIMD для векторных операций, а также ускорители сетевых операций и сжатия/декомпрессии данных. Дополнительно каждое ядро может иметь до 1,5 Мбайт сверхбыстрой памяти SRAM. Между собой ядра общаются напрямую.  В случае Grayskull e150 процессор работает в полной конфигурации со 120 ядрами и 120 Мбайт SRAM, объём внешней памяти LPDDR4 составляет 8 Гбайт (ПСП 118,4 Гбайт/с). Ускоритель выполнен в формате полноразмерной платы расширения с теплопакетом 200 Вт и интерфейсом PCIe 4.0 x16. У младшей модели, Grayskull e75, активных ядер только 96, их частота снижена до 1 ГГц, а пропускная способность внешней памяти при том же объёме снижена до 102,4 Гбайт/с. При этом теплопакет составляет всего 75 Вт, что позволило выполнить ускоритель в виде низкопрофильной платы расширения и обойтись без дополнительного питания. Чипы Wormhole тоже используют Tensix. В составе Wormhole n300 таких ядер 128, частота равна 1 ГГц при теплопакете 300 Вт. Объём SRAM составляет 1,5 Мбайт на ядро, а внешняя подсистема памяти включает 12 Гбайт GDDR6 и с ПСП 288 Гбайт/с. Wormhole n150 имеют такую же конфигурацию памяти, но оснащены только 72 ядрами Tensix и 108 Мбайт SRAM. TDP составляет 160 Вт. От Grayskull эти решения отличаются возможностью масштабирования путём прямого объединения плат. Также есть по паре сетевых интерфейсов 200GbE. Возможна работа с форматами FP8/16/32, TF32, BFP2/4/8, INT8/16/32 и UINT8. Чипы Tenstorrent Grayskull и Wormhole лежат в основе уникальных масштабируемых платформ собственной разработки — AICloud и Galaxy. В первом случае используются процессоры Grayskull, поскольку Wormhole на рынке должен появиться позже. Платформа предназначена в качестве аппаратной для ИИ и HPC-нагрузок в облаке Tenstorrent.  Каждый 4U-узел AICloud высотой содержит восемь карт (16 чипов) и способен предоставить в распоряжение пользователей от 30 до 60 vCPU и от 256 до 1024 Гбайт памяти, вкупе с дисковым пространством объёмом 100–400 Гбайт. Восемь таких узлов составляют стойку, а четыре стойки — кластер Server Pod. Четыре таких кластера объединены общей системой интерконнекта, управления и СХД (до 200 Тбайт), дальнейшее масштабирование уже выходит на уровень ЦОД. В Tenstorrent Galaxy упор сделан на возможность создания высокопроизводительных ИИ-систем с быстрым интерконнектом на базе Ethernet. Строительным блоком здесь являются 80-ядерные модули Wormhole. 4U-сервер вмещает 32 таких модуля, что в совокупности даёт 2560 ядер Tensix и 384 Гбайт глобально адресуемой GDDR6. Наличие 16 каналов 200GbE в каждом модуле обеспечивает производительность интерконнекта на уровне 3,2 Тбитс. На уровне стойки высотой 48U это дает 256 чипов Wormhole, общий объём SRAM в этом случае достигает 30,7 Гбайт, а GDDR6 — 3 Тбайт. Производительность стойки оценивается разработчиками в 20 Попс (Петаопс), а совокупная скорость интерконнекта — в 76,8 Тбит/с. Расплатой за универсальность и производительность станет энергопотребление, достигающее 60 КВт.

04.03.2024 [17:00], Руслан Авдеев

Евросоюз намерен добиться полупроводникового суверенитета, используя архитектуру RISC-VВ Евросоюзе активно инвестируют в инициативы, призванные обеспечить полупроводниковый суверенитет благодаря использованию открытой архитектуры RISC-V. EE Times сообщает, что инициативу курирует Барселонский суперкомпьютерный центр (Barcelona Supercomputing Center или BSC) — пионер в разработке европейских решений RISC-V. Страны ЕС беспокоит полупроводниковая зависимость от иностранных компаний, и это беспокойство усугубляется относительно недавним дефицитом чипов в мире. В то же время за использование в своих решениях архитектуры RISC-V никому не надо платить и ни у кого не нужно получать разрешений на её применение, поэтому технология так привлекательна для разработчиков. BSC представляет собой один из ведущих исследовательских центров Европы. Он играет ключевую роль в разработке чипов на архитектуре RISC-V и возглавляет несколько проектов, связанных с этой технологией, в частности, European Processor Initiative (EPI). В рамках инициативы EPI стоимостью €70 млн разрабатывается новое поколение высокопроизводительных процессоров. Связанная с BSC компания OpenChip должна найти коммерческое применение разработанным технологиям. BSC начал создавать собственные чипы семейства Lagarto довольно давно — первые 65-нм варианты представили ещё в мае 2019 года. Сегодня речь идёт уже о четвёртом поколении, которое будет выпускаться в соответствии с 7-нм техпроцессом. Центр работает и с другими европейскими компаниями и исследовательскими организациями над созданием комплексной экосистемы RISC-V, включающей ПО, ОС и компиляторы. Подобные инициативы должны снизить зависимость Евросоюза от американских и азиатских производителей — отсутствие в ЕС зрелой индустрии высокопроизводительных чипов расценивается как значимая уязвимость. Европа считает, что RISC-V — идеальная платформа для достижения суверенитета, при этом бесплатная. Впрочем, эксперты признают, что о полной независимости не может быть речи из-за сложности экосистемы полупроводниковой индустрии. Но у Европы есть большая база знаний и потенциал разработки новых решений, предпринимаются и шаги к организации производства. В BSC уже экспериментировали с Arm-процессорами, но после Brexit и приобретения компании Arm группой Softbank, выяснилось, что собственной региональной технологии у ЕС нет, тогда и обратили внимание на общедоступную RISC-V. В 2019 году Еврокомиссию убедили в необходимости начать выпуск чипов на этой архитектуре для суперкомпьютеров. В числе других европейских компаний, предлагающих RISC-V продукты, есть Gaiser, Esperanto Technologies, Semidynamics и Codasip, но они уделяют больше внимания процессорам и ускорителям, а не конечным готовые решения. По оценкам экспертов, в Евросоюзе компаний, работающих с RISC-V, пока недостаточно. Тем не менее, организаторы новых инициатив предостерегают от нереалистичных ожиданий и призывают к стратегическому сотрудничеству — для производства требуются не только разработки, но и сырьё, высокоточное оборудование, и др. Европа может рассчитывать на выпуск решений в пределах 7-нм, более современные техпроцессы пока слишком дороги. Впрочем, ЕС уже добился значительного прогресса в достижении полупроводникового суверенитета с помощью RISC-V. |

|