Материалы по тегу: jedec

|

17.10.2023 [19:00], Алексей Степин

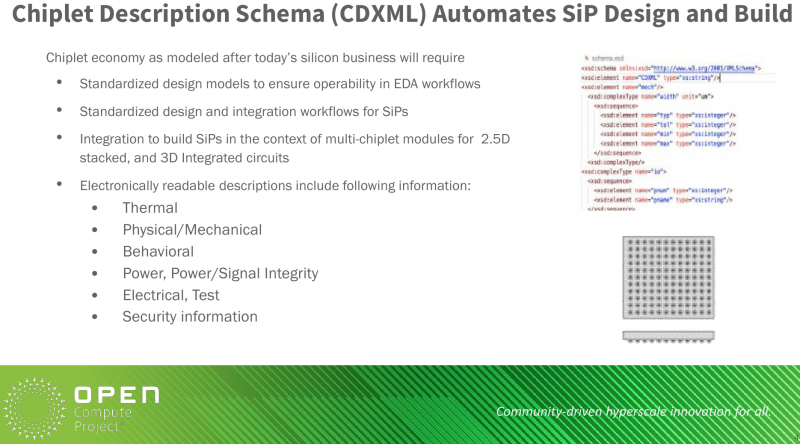

OCP и JEDEC намерены построить «чиплетную экономику»Сейчас уже очевидно, что ставка на огромные монолитные кристаллы в деле производства сложных чипов себя исчерпала и будущее за чиплетными технологиями. Но каким будет это будущее? Комитет стандартизации полупроводниковой продукции (JEDEC) и организация Open Compute Project на проходящем в настоящее время мероприятии 2023 OCP Global Summit объявили о сотрудничестве с целью выработки единого набора стандартов и унификации чиплетной экосистемы. Такой альянс способен задействовать сильнейшие стороны участников: влиятельность JEDEC в деле установления мировых стандартов в области микроэлектроники и опыт OCP в разработке устройств системного уровня, способствующий появлению новых технологий и рынков. Это позволит избежать фрагментации и излишних затрат, вызванных дублированием усилий при разработке новых устройств. OCP уже располагает спецификациями CDXML (Chiplet Data Extensible Markup Language), включающими стандартизированное описание, которое можно использовать при работе с современными средствами автоматизированного проектирования электроники (EDA). CDXML включает в себя следующие данные:

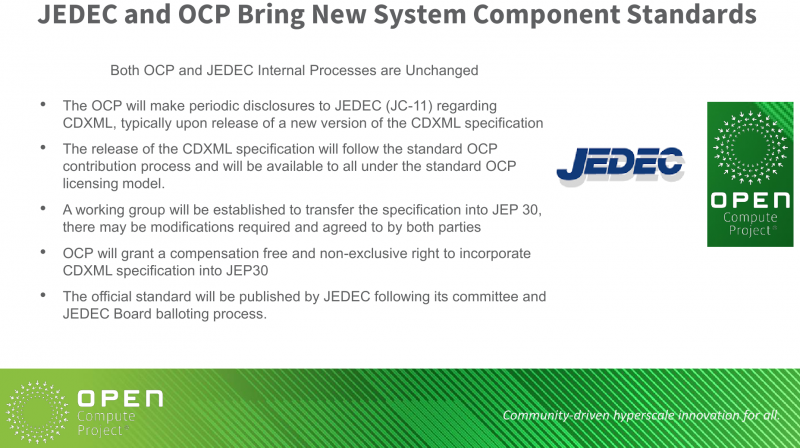

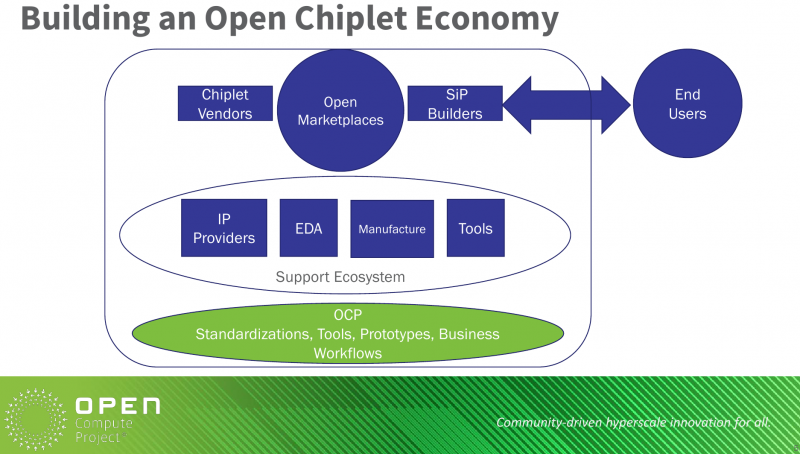

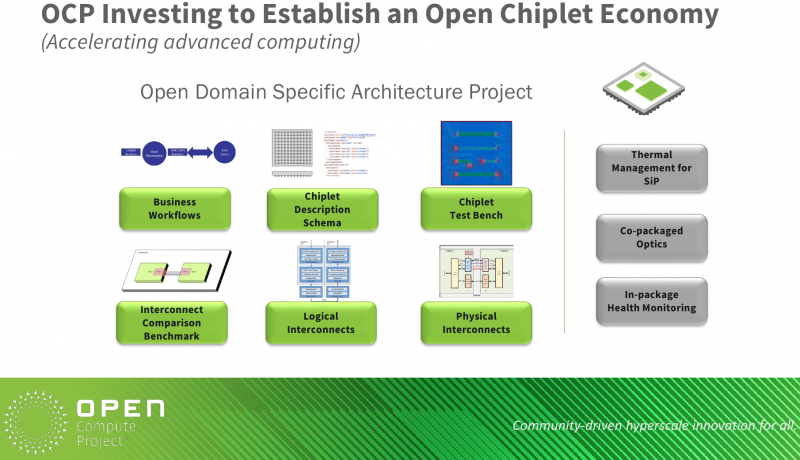

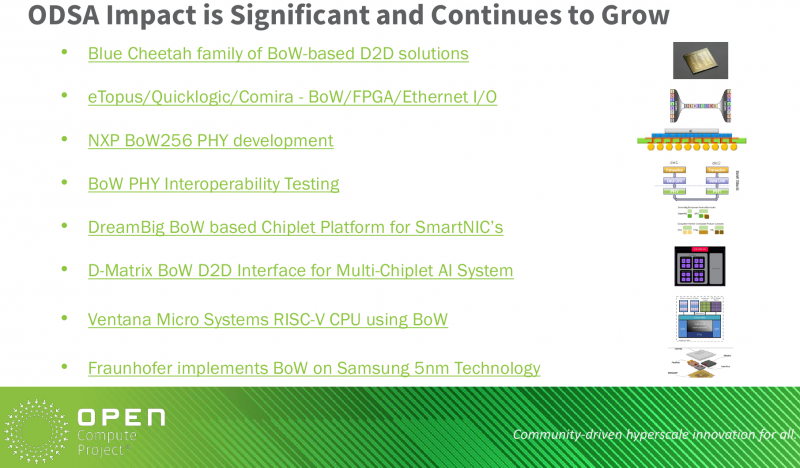

Это облегчит обмен данными между разработчиками чиплетов и их клиентами, благо уже сейчас идёт процесс интеграции CDXML в правила JEDEC JEP30 (Part Model Guidelines), описывающие процесс такого обмена. Внутренние процессы OCP и JEDEC сотрудничество не изменит, но OCP планирует регулярные поставки новых данных, относящихся к CDXML в JEDEC (JC-11) — обычно это будет связано с выпуском обновлённых версий CDXML. В соответствии с правилами лицензирования, принятыми OCP, новые данные будут доступны всем участникам консорциума. Для ускорения интеграции новых спецификаций в стандарт JEP30 будет сформирована специальная рабочая группа, в задачи которой войдёт в том числе и достижение обоюдной договорённости о внесении необходимых изменений. Официальный стандарт будет публиковаться решением комитета JEDEC в соответствии со стандартной процедурой голосования. Создание единых спецификаций CDXML открывает дорогу целому новому направлению в разработке чипов — так называемой «чиплетной экономике» (Open Chiplet Economy), в которой разработчики чиплетов смогут посредством открытого рынка взаимодействовать с производителями чипов. Такой рынок станет возможным именно благодаря созданию унифицированной экосистемы, за поддержание которой в актуальном состоянии и будет отвечать OCP. В рамках такой экономики любой проект сможет пройти от стадии описания чиплета к его тестированию с помощью специальной платформы, оценке производительности систем интерконнекта, интеграции разнородных систем, и, наконец, сборке готового решения с оценкой его термальных характеристик. Предполагается также возможность использования фотоники и наличие интегрированных средств диагностики. В рамках проекта OCP Open Domain Specific Architecture (ODSA) уже достигнуты серьёзные успехи, в число которых входит разработка высокоскоростного конфигурируемого интерконнекта Blue Cheetah класса BoW (Bunch of Wires), создание платформы DreamBig для «умных» сетевых адаптеров, использование BoW-интерконнекта в процессоре с архитектурой RISC-V и даже интеграция BoW-технологии в 5-нм техпроцесс Samsung. А сотрудничество OCP с JEDEC должно ускорить формирование «чиплетной экономики» и избежать ошибок, свойственных закрытым стандартам и платформам.

04.04.2023 [20:09], Сергей Карасёв

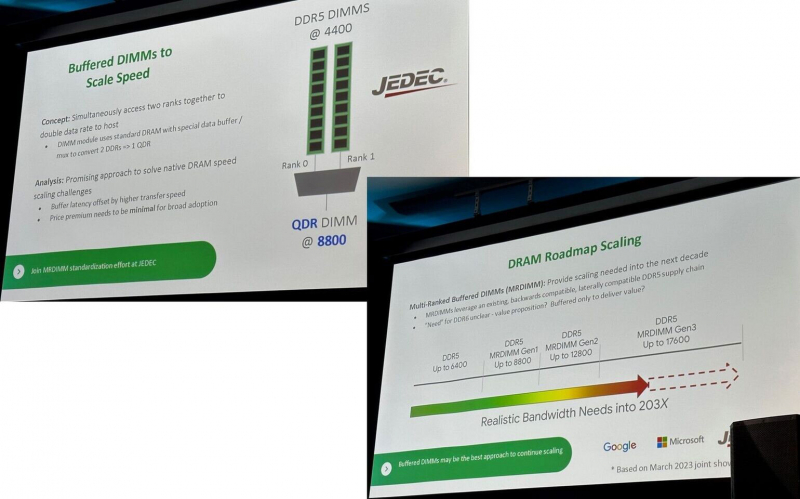

AMD и JEDEC готовят сверхбыстрые модули памяти DDR5 MRDIMMКомпания AMD и ассоциация JEDEC, по сообщению ресурса HotHardware, проектируют модули оперативной памяти DDR5 RAM нового типа — MRDIMM, или Multi-Ranked Buffered DIMM. Речь идёт об изделиях с многоранговой буферизацией, ориентированных на серверное оборудование. Модули обеспечат высочайшую скорость передачи данных — до 17 600 МТ/с. По задумке разработчиков, решения MRDIMM будут объединять два модуля DDR5 с возможностью одновременного использования двух рангов. Таким образом, в случае, например, пары модулей DDR5 со скоростью работы 4400 МТ/с можно будет получить эквивалентную производительность до 8800 МТ/с. Для использования такой схемы потребуется специальный мультиплексор между оперативной памятью и CPU. Он позволит направлять в сторону процессора вдвое больше информации по сравнению с традиционными архитектурами. Аналогичный подход применяет SK hynix в своей памяти DDR5 MCR DIMM. Такой подход обеспечивает удвоение скорости работы подсистемы ОЗУ без увеличения быстродействия самих чипов памяти. По всей видимости, буферизация с применением мультиплексора добавит некоторую задержку при передаче информации, но она будет компенсироваться более высокой скоростью работы сдвоенных модулей. Память MRDIMM первого поколения сможет функционировать с показателем 8800 МТ/с, второго — 12 800 МТ/с. А после 2030 года ожидается появление решений со скоростью до 17 600 МТ/с. Новая память может стать альтернативой дорогостоящим продуктам HBM, которые масштабируются только до определённого значения ёмкости. При этом объединение двух модулей DDR5 избавит от необходимости добавлять дополнительные ОЗУ-слоты на серверные материнские платы. Как в случае MCR, подход MRDIMM всё так же напоминает DDIMM/OMI и FB-DIMM.

24.01.2023 [17:00], Владимир Мироненко

OCP и JEDEC будут вместе разрабатывать стандарты для чиплетовНекоммерческая организация Open Compute Project Foundation (OCP), специализирующаяся на разработке оборудования для ЦОД на основе открытых спецификаций, и ассоциация JEDEC Solid State Technology Association, мировой лидер в разработке стандартов для микроэлектронной промышленности, объявили о новом соглашении о сотрудничестве с целью включения технологий, разработанных с использованием одобренных OCP спецификаций в стандарты JEDEC. OCP Chiplet Data Extensible Markup Language (CDXML), созданный с целью стандартизации описания компонентов чиплетов, войдёт в состав JEDEC JEP30 (Part Model Guidelines). Используя обновлённый стандарт JEDEC, который, как ожидается, будет опубликован в 2023 году, производители микросхем смогут предоставлять стандартизированное описание компонентов, что позволит задействовать системы автоматизации проектирования и сборки (SiP) чипов. Описание будет включать информацию о тепловых характеристиках, физических и механических требованиях, особенностях поведения, требования к питанию и целостности сигналов, информацию о тестировании чиплета в упаковке и параметры безопасности.  OCP уже несколько лет инвестирует в исследования, стимулирующие экономику «открытых чиплетов» в рамках своего проекта Open Domain Specific Architecture (ODSA). «Мы рады заключить этот альянс с JEDEC, чтобы работа, выполняемая в ODSA, стала частью глобального международного стандарта, который продвигает отрасль», — сообщает OCP. В свою очередь, JEDEC отмечает, «JEDEC и OCP едины в мнении, что стандарты, разработанные в рамках открытого сообщества и отраслевого сотрудничества, необходимы для развития эффективных рынков». Аналитики Yole Group отмечают, что цепочка поставок полупроводников разнообразна, так как должна обеспечивать выпуск электронного оборудования для различных целей и отраслей. При этом поставщики чипов используют крайне разнородные платформы, а производство чипов становится всё более сложным и дорогостоящим. Именно поэтому производители начали использовать чиплеты. Однако ни один из поставщиков не обладает обширным опытом для обслуживания всех отраслей. Внедрение открытых стандартов «имеет решающее значение для ускорения развития экономики чиплетов», считает Yole Group.

25.08.2022 [10:00], Сергей Карасёв

Консорциум CXL и JEDEC подписали меморандум о взаимопониманииКомитет инженеров в области электронных устройств JEDEC Solid State Technology Association и консорциум CXL (Compute Express Link) объявили о подписании меморандума о взаимопонимании. Цель — сотрудничество в области DRAM и технологий постоянной памяти. JEDEC специализируется на разработке стандартов компьютерной памяти. В работе комитета принимают участие такие известные компании, как AMD, Elpida, Hynix, IBM, Infineon, Micron, Samsung, Toshiba, Texas Instruments и другие.

Источник изображения: Gerd Altmann / pixabay.com В свою очередь, консорциум CXL продвигает одноимённую технологию — высокоскоростной интерконнект, обеспечивающий взаимодействие хост-процессора с акселераторами, буферами памяти, умными устройствами ввода/вывода и пр. По условиям договора, JEDEC и CXL сформируют совместную рабочую группу, которая будет отвечать за обмен информацией, требованиями и рекомендациями. Это поможет обеим организациям в разработке стандартов, которые будут дополнять друг друга. «При поддержке со стороны десятков ведущих отраслевых компаний данное сотрудничество позволит обеим сторонам оптимизировать разработку стандартов и поможет JEDEC в создании отдельных стандартов, предназначенных для модулей памяти и компонентов CXL», — говорится в совместном заявлении. |

|