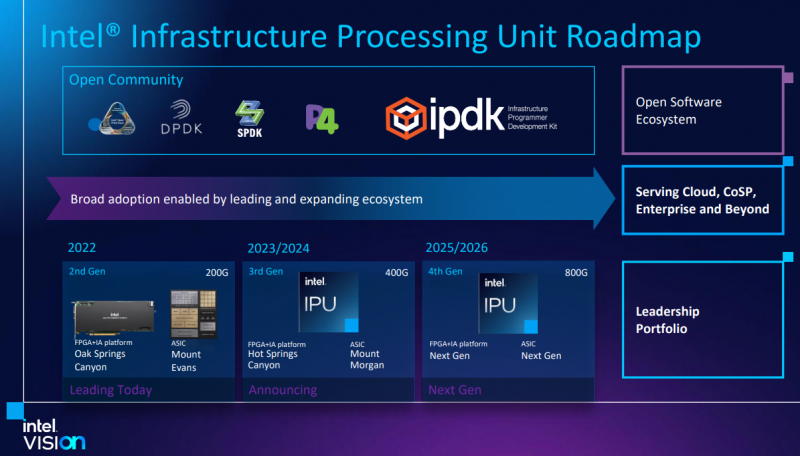

На мероприятии Vision 2022 компания Intel продолжает рассказывать о текущих и грядущих новинках, и на этот раз речь пойдет о так называемых об IPU (или DPU терминах других производителей). Новые планы Intel простираются до 2026 года и включают в себя создание ускорителей, рассчитанных на работу в сетях 400GbE и 800GbE.

Первое поколение IPU (100/200GbE) Mount Evans использует ASIC и ядра Arm Neoverse N1. Mount Evans разрабатывается совместно с Google и Microsoft. Есть и серия Oak Springs Canyon, в которой компания применила Xeon D и FPGA Agilex. На смену им в будущем придут Mount Morgan (ASIC) и Hot Springs Canyon (FPGA). Оба варианта ожидаются в 2023–24 гг. и позволят Intel освоить скорость 400 Гбит/с. Добраться до 800 Гбит/с планируется в 2025–2026 гг., и тоже при помощи ASIC и FPGA. О развитии «обычных» SmartNIC на базе FPGA компании рассказывать пока не стала.

Для разработки предлагается использовать открытый фреймворк Infrastructure Programmer Development Kit (IPDK), который можно использовать для IPU/DPU, коммутаторов и даже обычных CPU. В ближайшее время IPU Intel будут «сопровождать» коммутаторы на базе Tofino 3, которые тоже поддерживаются IPDK, что позволит создать сквозную цепочку работы с сетевым трафиком. И наличие развитой программной экосистемы может сыграть решающую роль, поскольку занять свою нишу пытается целый ряд компаний: AMD (Pensando и Xilinx), Chelsio, Fungible, Kalray, Marvell, Nebulon, NVIDIA.

Источники: